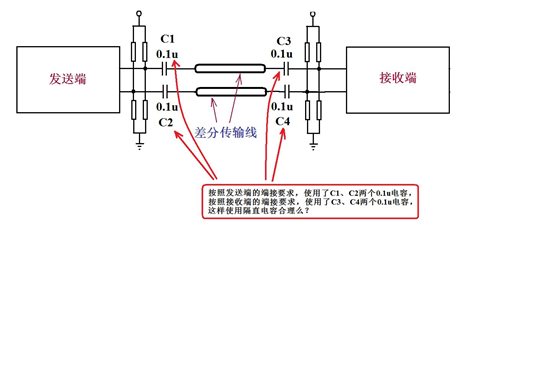

差分传输线上 隔直电容的使用

时间:10-02

整理:3721RD

点击:

按照 发送级芯片的DATASHEET要求,应该在发送级芯片的输出端 使用端接电阻、隔直电容;而按照 接收级芯片的DATASHEET要求,应该在接收级芯片的输入端 使用端接电阻、隔直电容。

这样一来,就在同一根传输线的两端,各有1个隔直电容,但是隔直只需要1个电容即可。

如果只用1个隔直电容,那么位于传输线的哪端更合理呢?

详见附图

James,您好

差分线的端接电路部分和发送端以及接收端芯片的内部特性相关, 不能简单论之。

如果芯片本身支持共模电压自建,那外部的上下拉电阻就不需要。如果发送端输出是LVPECL信号,需要接地电阻。

同时也有芯片接收端内部集成电容的情况,这样也不需要外部电容。

根据我们的经验,信号链路上即便发射端和接收端都放置了AC耦合电容(通常为0.1uF),不会对信号的完整性带来什么大的影响。

James,

你的发送和接收在两个板上还是在同一个板上? 传输的是什么协议的信号?PCIe? 数据速率是多少?

典型的,在同一个板上的差分信号传输,电容放在哪端都影响不大,源端的上下拉偏置负载是比如LVPECL输出需要的,

末端的上下拉是提供偏置电压以及终端匹配,典型是差分100ohm.

希望有帮助。

regards,

Ivan