TSB41AB3的I/O接口

现在做工程项目时候用到这款芯片,想知道芯片I/O接口接受的外部信号有没有直流偏置,以及能够接收的信号的电平范围,最后还有接口是什么形式的,非常感谢!

IO口的电气参数你可以参考下datasheet Page11~13的表格:http://www.ti.com/lit/ds/symlink/tsb41ab3.pdf

如有其它问题,可继续讨论。

您好,我看了一下,是我找的东西,您能不能解释图片中这三个的意思,以及其中有没有能作为数据电压信号输入的电平范围,谢谢了!

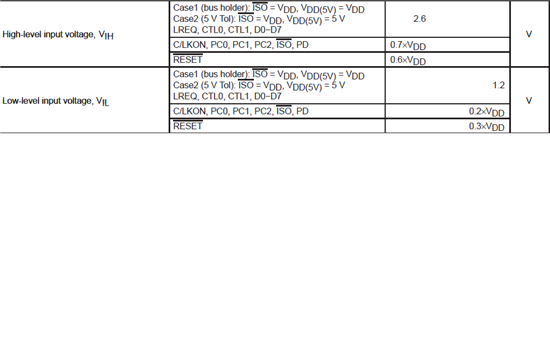

信号输入的电平范围即为如下图所示,可以看出,并不是标准的3.3V TTL 高低电平的标准。

哦,知道了,再请问一下,就是该芯片数据接口接收差分信号是否有共模信号,也就是输入的信号有没有直流偏置呢?谢谢了!!!

您能解释一下上图中的三个电平范围吗?谢谢了!!!

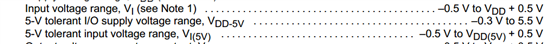

首先这几个参数都是指的最大值absolute maximum ratings,如果在使用器件的时候,建议参考推荐的电气特性表格“recommended operating conditions”。

第一,指的是输入引脚能够承受的最大电压范围,比如3.3V供电时,输入引脚的范围为-0.5V~3.8V。

第二,-0.3V~5.5V的电压范围指的是VDD-5V这个引脚的最大电压范围。

第三,−0.5 V to VDD(5V) + 0.5 V这个范围指的是由VDD-5V引脚供电的电路的IO口的电压范围,是5V tolerant。

不知这样解释你清楚了没

哦,明白了,谢谢了!我还有一个不明白的地方,就是这个芯片一般和链路层中的tsb12lv01b相连,通过线缆接收链路层芯片发出的差分信号上有没有共模电压?

以及这个信号的范围是多大时tsb41ab3芯片能够正确的接收呢?我看了您给的资料好像没找到,谢谢了!

您好,您能不能解释一下这个source power node和nonsource power node的意思吗?谢谢了!

其实你的这个问题在datasheet Page11中也提到了,cable的共模电压范围为0.4706~2.515V,差模信号电压范围118mV ~260mV .

关于cable中的直流偏置,datasheet中也有提到,cable Bias(TPBIAS)为1.8V的偏置电压。

这个具体解释可参考下IEEE1394a-2000 Spec的Section 4.2.2.2。字面上的意思就是一个节点mode是否使用的是cable power,是的话就是source

power node,不是的话就是nonsource power node。具体的你可参考下1394的Spec。

非常感谢!您说的这个cable输入信号的电压范围和上图这个接收器的输入信号阈值有什么不同吗?

您好:

我想问一下共模电压不是一个不变的直流电平吗,为什么这里的cable的共模电压还是一个范围呢?

谢谢!

这里的cable输入信号电压的范围是在Driver disable的测试条件下,而之前说的cable的输入电压的范围则没有这个条件。

确实是一个固定不变的电平,这里给出的范围意思是在这个范围内的任何一个电平值都可以,或者说不同应用条件下共模电压不同,但只要在这个范围内,cable都能适用。

谢谢kailyn

您有没有关于driver和receiver的电路结构的资料吗,我想具体仿真一下这两个接口的输入输出电平大小?谢谢了!

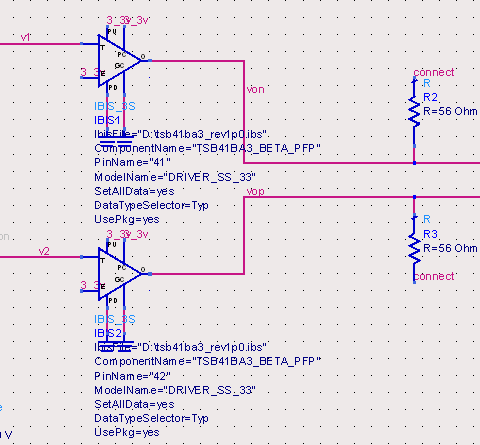

附件是TSB41AB3的IBIS模型,你可以用 HyperLynx进行仿真。

3806.tsb41ba3_rev1p0.ibs

谢谢了,kailyn!

您给的模型我已经仿真过了,我想问一下仿真出的驱动器\接收器输出\输入的电压值是不是和实际电路中的电压值相同呢?

还有在实际工程中物理层芯片和连接器中间有没有加隔离变压器呢,还要麻烦您给一张它们之间实际工程电气连接的图?

非常感谢!

仿真的是和实际电路的电压值是一样的,实际电路的电气特性也是和datasheet中给出的电气参数是一致的。另外,我们没有物理层和连接器之间的电气连接图呢。

非常感谢了!

该ibis模型仿真差分信号中,TPB+和TPB- 端输入的电平一样吗?它们的电平值范围是多少呢?也就是下图中v1,v2的值。还有就是实际电路中驱动器驱动一对差分信号线而仿真中需要需要两个这样(如下图所示),这样仿真的输出电压会不会和实际的值不一样呢?谢谢了!