LVPECL和CML电平转换

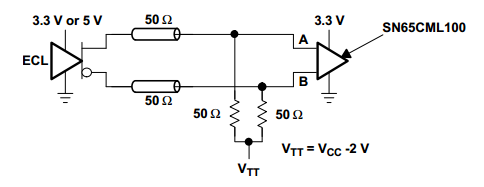

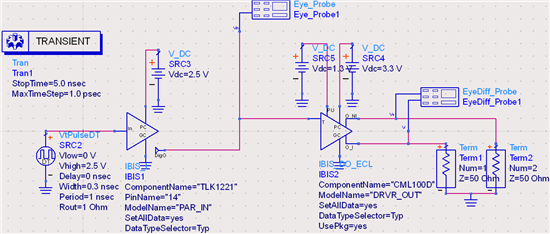

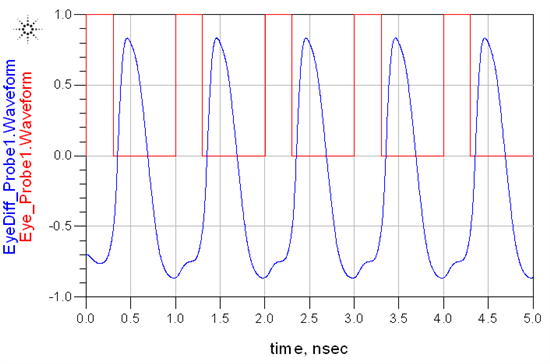

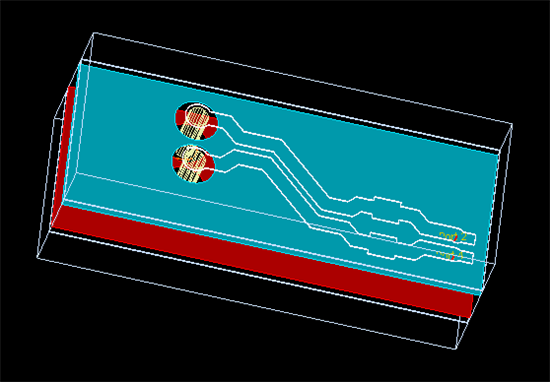

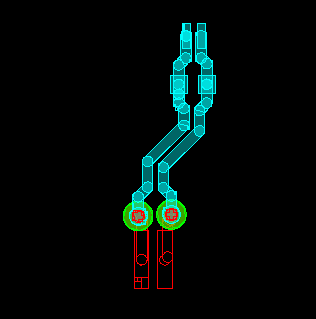

采用TI公司的tlk1221芯片做并转串的变化,带宽为600MHz,串行输出为LVPECL电平,芯片的供电电压是2.5V,由于项目中需要得到CML电平,所以其中采用TI公司的sn65cml100做电平转换。综上所述为LVPECL到CML电平的变换,另外TI公司提供了这两款芯片的IBIS模型,由于频率相对较高,在电平转换的时候需要相应的端接来尽量保证信号的完整性,在做PCB板之前用Hyperlynx做了模型的前仿真,采用的电路是sn65cml100提供的电路,如下图1所示。

图1 电平转换图

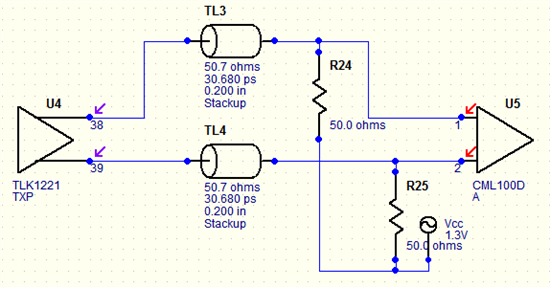

则在Hyperlynx中的图如下图2所示,其中驱动器为tlk1221:

图2 Hyperlynx图例

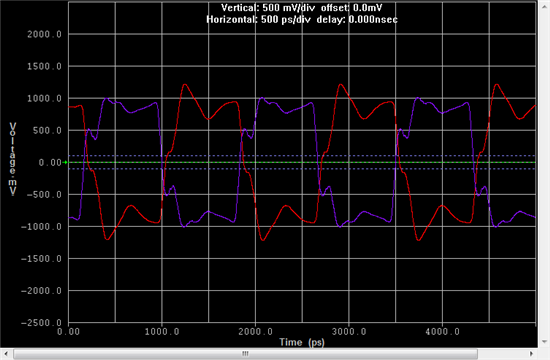

最终得到输入和输出的差分信号为下图3所示:

图3 Hyperlynx差分信号仿真图

由上图3可以看出这个信号反射十分严重,上图中红色线为输出端信号,紫色线为输入端信号,我个人分析可能是阻抗不连续导致,其中根本没法得出不连续的点在哪里,唯一可能的是tlk1221的输出电阻,因为LVPECL信号电路输出电阻很小,但是我也在输入端串了电阻仿真过,得到的波形也是很不理想,所以希望各位帮忙分析分析,问题可能出在哪里,或者是tlk1221作为驱动器的时候,匹配图不能按照sn65cml100中所给出的参考电路仿真,我想这样去做板的话应该是没法使用的吧!

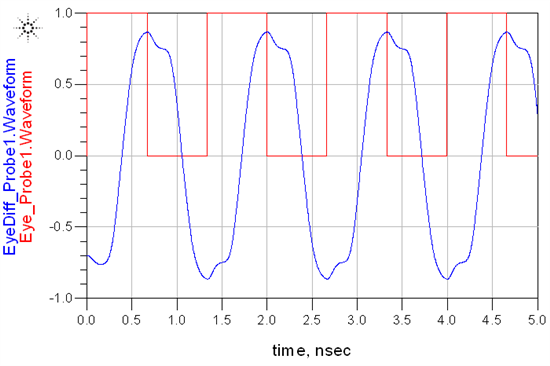

我用ADS仿真了一下,直接连没有发现什么问题,所以应该不是TLK1221的问题,不知道TL3那段cable是根据什么得到的?看样子好像这段里的阻抗不匹配造成的

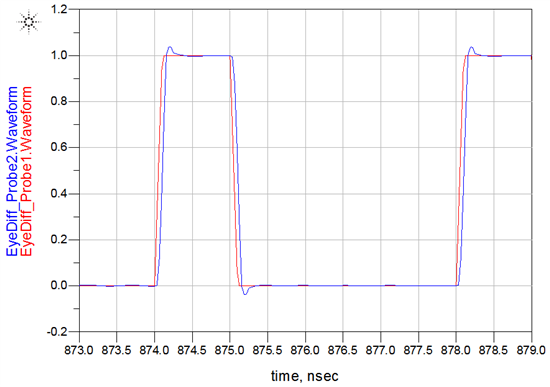

仿真结果如下,两个scope的图,红的为中间线,蓝的是cml100的输出

更正一下,频率应该改成这样

波形应该是这样的

您好,谢谢您的回复。我试着仿了一下您提供的方案,用ADS是没有问题的,但是在芯片之间是需要加上传输线的,阻抗控制在50欧姆。

另外有两个问题请教您:

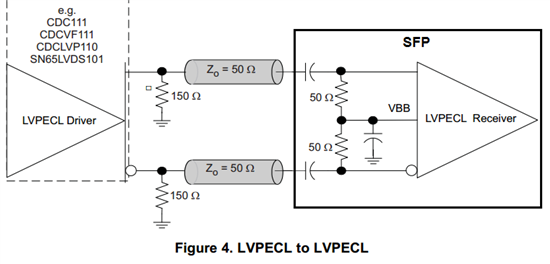

(1)我们在使用TLK1221这款芯片的时候,它的数据手册里面提到高速串行总线(RXP、RXN、TXP、TXN)和LVPECL是兼容的,我想请问您一下这个和LVPECL是同一个标准吗?因为在和光纤模块通信的时候需要进行端接,如果不是LVPECL电平的话电路板设计可能就有麻烦了,因为我们是将TXN和TXP通过50欧姆电阻连接到GND了,然后通过AC耦合和SFP光纤模块相连。

(2)TLK1221这款芯片的RXP、RXN、TXP、TXN这几个管脚和标准的SFP高速管脚方面进行差分互连十分的不方便,需要好几个过孔,因为管脚都是错位的,所以我们打算将这款芯片的RXP和SFP光纤模块的RXN相接,也就是将差分信号反着接,请问一下这样可以的吗?谢谢您了!

Shuai Liu,

【1】这个接口是可以和SFP模块连的。SFP标准规定是内置AC耦合,可以接收差分幅度250~1200mV的信号,而TLK1221的输出差分幅度是600~1100mV,所以可以直接连接。建议用下面的接法,源端用150给LVPECL偏置。

【2】这个芯片没有极性纠正功能的,所以不能这样反着接。您还是加几个过孔吧,注意控制好过孔附近的阻抗就行。

Dylan

AFAA of South China

您好,谢谢您的指导,对于第二个问题,加入反着接了是不是接收到的10bit并行数据是反向的,又或者压根就不能反着接?因为TLK1221串行输出频率在600M~1.3G,所以添加过孔进行差分互连的话,可能导致阻抗的不连续,导致信号的反射,这样处理起来就更加麻烦了,另外,请问您:如果添加小点的过孔,是不是对1GHZ以下的差分信号影响并不是很大?谢谢!

LVPECL反接是可以的,但是数据就是反向的了。过孔问题要看实际情况了,过孔小点是会减小分布电容,但主要还是看实际阻抗变成多少,另外还要注意的是过孔换层的时候电流路径带来的问题,下面两篇应用手册里讲了一些关于Via的处理。不知道你可不可以对这两条线做一下PCB仿真?这样会比较好。如果不涉及保密的话,您把PCB发给我看一下。

4667.slyp173.pdf

1172.scaa082.pdf

Dylan

AFAA of South China

谢谢您的回复!附件当中我这块板的网表和.brd文件,设计软件是 Cadence Allegro,另外还想请问您,用什么软件可以仿真这2对差分线?Allegro自带的SI分析吗?谢谢您!

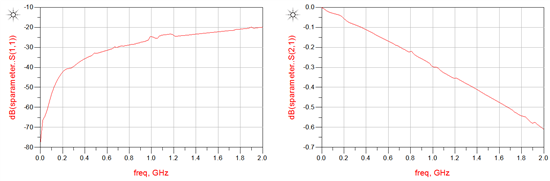

关于您说的高速管脚和SFP接口管脚错位的问题,我看图中好像顺序是对的,不知道您是遇到什么问题了。从PCB看,1G的信号对于这么短的走线是很轻松的,问题不大,我仿真了一下RX差分对,挺好的。

我是用ADS里的momentum mirowave来做PCB仿真,allegro的没用过。

这是输入和输出波形,还是不错的。

谢谢您的解答!

我在画板之前是用Hyperlynx做了前仿真,但是波形不理想,后来也就没有考虑直接画板了,我所担心的问题是怕PCB板做出来的波形十分的不理想,没有相关的仿真结果的话也不好分析。仿真我用的是TI给出的IBIS模型。谢谢您了,我们先按照您给的方法做做,接着把PCB做出来实测看看,有问题在向您请教,谢谢!

TLK1221是一颗被广泛应用的serdes,可提供快速锁定功能,尤其适合PON等应用。

对于你提到的问题,由于TLK1221采用类似LVPECL电平但又比LVPECL具有更低功耗的VML电平,发送端外围电路不需要下拉电阻,如上建议,跟SFP可以直接互联即可。

您好!谢谢您的回答!但是这块芯片对于手工焊接来说好像有一定的难度,关键是这块芯片底下的大焊盘。

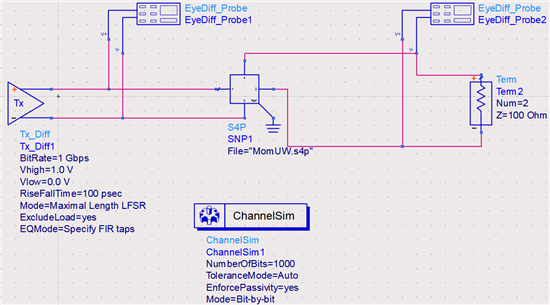

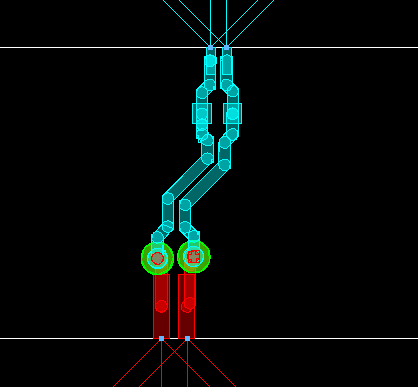

您好!谢谢您的回答,我试着用您提供的方法进行了仿真,从gerber文件导入到momentum之后的波形如下图所示,我所使用的是ADS2009,我想请问您,接下来还需要如何进行设置才可以得到您仿真的这样结果,您可否提供相关的仿真经验,或者相关的资料?谢谢

您好!我在momentum中进行了差分线的仿真,图形如下所示,我想请问您:

(1)您仿真这对差分线的时候有没有将过孔考虑进去?就是信号进行了换层。我按照您说的方法去仿真是从TOP到BOTTOM得到的S参数。

(2)您有没有给这对差分线指定相应的参考平面?如果没有,您是怎么设置的?我在仿真的时候也没有给定参考平面,就是将Gerber导入之后进行层叠设置,然后仿真。我只导入了TOP,GND,POWER,BOTTOM和DRILL,因为是4层板。

下图(1)所示为仿真的差分线,蓝色箭头为顶层差分PORT,红色箭头为底层差分PORT。

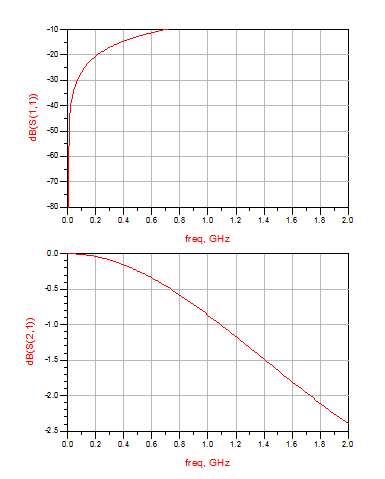

下图(2)所示为图(1)仿真得到的S参数,和您仿真的相比,好像差很多,我不知道是不是我哪里设置的不对。

希望您能够提供相应的指导,万分感谢!

图(1):差分线信号输入输出

图(2):差分线仿真得到的S参数