关于TI高速485芯片在应用中的问题

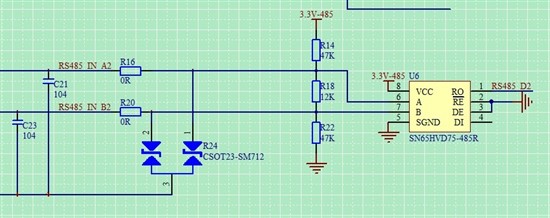

发个帖子问一下 我的项目每个板子使用到4路485 , 采用的是TI的SN65HVD75(官方称最高25M速率)芯片,我最高一路速率达到10M,其他的3路都在1M一下

但是现在遇到的问题是通讯信息不准确,有时正常有时不正常,现在排查到的最可能是线的阻抗不匹配,因为当节点接了有2-3个时就可能出现传输的信息不准确,而且总距离也就4-15m的范围

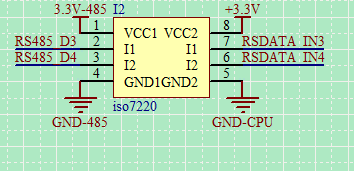

我485已经是独立的一路电源且采用电源隔离模块,在传输也使用了TI的ISO7220隔离

现在依然查不出什么问题 想问问论坛大家帮我看看是不是电路设计不合理,还是还有其他可能的问题

因为这个小批量了,发现接的多就出现这个通讯的问题,焦头烂额。。。希望有经验的大侠帮帮忙,

图上的电路是发送电路和接收电路 120欧的电阻只在第一个和最后的板子才焊接上

补充一下 485官方数据是20M

可以加一个共模噪声滤波器,同时把上拉和下拉电阻换掉

上下拉电阻使用523欧左右更好防止总线失效

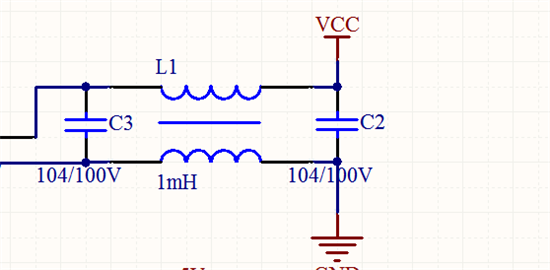

这个我可以换电阻 但是关于再加一个噪声滤波器 我有2路输入电压 24V和5V 都需要加吗 还是只在5V那一路加就可以

还有就是针对这个485应用 滤波器有什么具体的性能参数吗 因为我现在不清楚需要选择电感电容的大小 有没有经验值? 这个是我准备在5V进去的电路

感谢Carter Liu 的指导

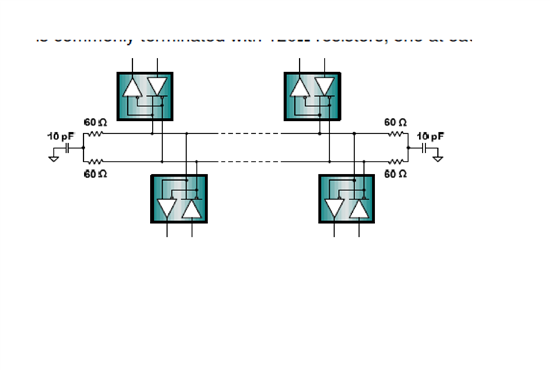

你好,你理解的不对,我不是说电源上加,而是在差分线上,如图:

终端匹配电阻以这种2个60欧形式组合,这两个60欧电阻要用精密电阻以降低共模噪声,同时你的传输线最好使用屏蔽双绞线,地环路设计要合理

您这个应用手册我昨晚看过 但是忘记在文档名字了 刚刚一直没找出来 能不能提供个下载地址?

哦 这样的话PCB要重改了。。。。。。。。。。

双绞线是肯定有用的,那上面说的上下拉电阻还需不需要呢?

上下拉电阻是需要的,但是其值应该参考这个应用手册:4274.RS-485 Design Guide.pdf

OK 我到时去现场试试到时把结果告诉大家

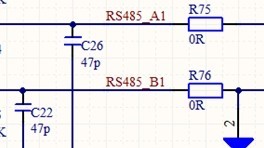

再问一下 像图中的这里的电阻电容是否可以保留

这个保留或者使用焊锡丝直接短路都可以,影响不大。另外芯片在板子上的退耦电容要加上,最好是加两个,一个10uF滤波一个0.1uF退耦。板子上的差分线要平行等长至连接头

你的问题解决了吗?终端匹配电阻120ohm应该尽量靠近接收端。

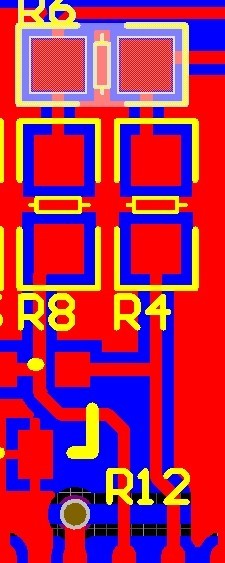

还没试 器件还没到 这是我布线的距离 图中白色的是120欧电阻

我在PCB器件位置跟上面的原理图类似 你的意思是要PCB的器件位置要如同下面原理图这样?

我需要到客户现场试 因为在公司 用LED模拟继电器是可以的 但是在现场 接入继电器通讯就乱了

现在一直在电源干扰和阻抗匹配这里纠结 不知道具体是哪里出问题

很遗憾的告诉大家 我采用上下拉电阻523欧 60.4欧1%精度 220p电容

按上述方法连接 一个一收一发 LED模拟实验可以 中间接多一台节点就出现问题了,通讯解码出来就错误了

头大啊~~~。。。。 还有大大们有什么经验么