你好,请教一下LMK04906支持的最小的输入参考频率是?

如果使用了1MHz的参考输入时钟,是不是就意味着LOS_TIMEOUT只能选择 1200ns/420kHz?

否则LOS_TIMEOUT的其他选项(206ns/2.5MHz,52.9ns/10MHz,23.7ns/22MHz)会导致LOS发生而无法锁定是吗?

多谢~~

根据loss of signal的描述来看,只有在enable los_timeout的时候才要考虑最小的reference,

也就是detect 的时间至少于半个周期,(如2.5MHz 半个周期在200ns 然后留有一定的误差量)。

所以1MHZ只能选用1200ns/420kHz mode.

你好,还有个问题:

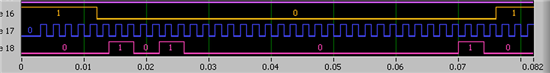

readback功能找不到read信号的头,后来用示波器看来一下时序关系,发现读和写是同时的,只相差一个CLOCK,并没有像附件描述的时序关系,这个是怎么回事呢?而且发现更改READBACK_LE不会更改LE的脉冲宽度,一直是窄脉宽,这个是软件的问题吗?多谢~

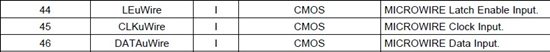

没看到图,看您的描述有些奇怪。手册中介绍LEuWire是输入引脚,readback_LE 仅是设定在HIGH或LOW 做readback

不好意思,估计我没说清楚,补充一下:我想问在readback情况下,我即便设置readback_LE=HIGH,测试出来的记过还是readback_LE=0的波形,即LOW时做readback,而不是HIGH时做readback,这个是怎么回事呢?非常感谢~~

没有看到您的图片,最好上传一下您的时序图,另外请注意手册47页关于readback的介绍,readback_LE 配置是一方面,LEuWire 输入信号的控制是否正确。

...To perform a readback operation first set the register to be read back by programming the READBACK_ADDR register. Then after any MICROWIRE write operation, with the LEuWire pin held low continue to clock the CLKuWire pin. On every rising edge of the CLKuWire pin a new data bit is clocked onto the any pins programmed for uWire Readback. If the READBACK_LE bit is set, the LEuWire pin should be left high after LEuWire rising edge while continuing to clock the CLKuWire pin...

你好,请问你之前遇到的PLL2锁定不了的问题解决了吗,我现在也遇到了同样的问题、、、

描述一下具体情况?

1. 下载工具是 CODELOADER 还是 MPU 还是FPGA?

2. LD管脚的波形?

3. 下载工具 若是MPU或者FPGA的话,具体的下载时序?

4. PLL2失锁的情况下,输出时钟的频率是多少?

谢谢回复。

1、我是利用Labview产生的一个SPI时序。

2、LD管脚应该是低电平,接在该管脚的LED灯没有亮

3、失锁情况下,设置CLKOUT divder全1,输出的时钟是1.87MHz

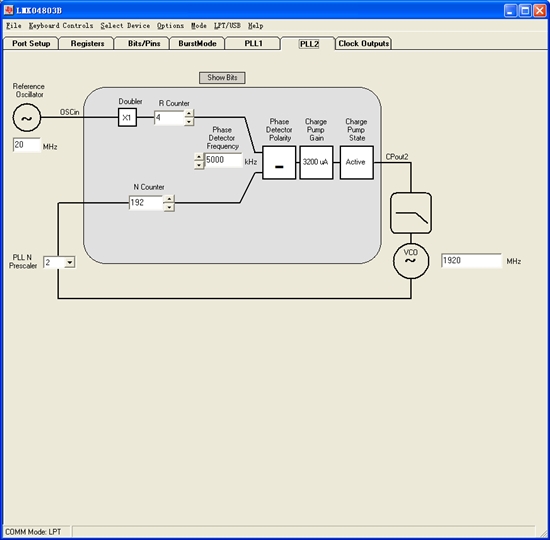

PLL2的那些N、R参数值,是参照 CODELOADER里的值设置的:

现在不清楚PLL2失锁,是不是还需要配置某个寄存器的值 才行,谢谢。

那你用CODELOADER下载的话,能够成功么?

还没有试过 今天试一试

我的解决了

我之前一直是uwire接口通讯不是很正常,后来在LE/DATA/CLK中间串接个电阻通讯就可以了,之后PLL2也锁定了。不知道为啥必须加电阻

我怀疑之前配置的下发有问题,导致一些配置不对

你的接口通讯有异常吗?

你是通过MCU配的吗,是不是MCU输出高电平是5V 所以要加个电阻分压,我前天刚开始搞,感觉应该是配进去了。另外请教一下怎么能判定,PLL2锁定?我之前是利用20M的参考频率,当时判断如果PLL2锁定,把参考频率变为21M,输出频率会明显改变,现在是输出频率并没有变化,PLL2应该是没有锁定。

是不是MCU输出高电平是5V 所以要加个电阻分压 ------ 这个要按照 你所用的MCU 的I/O标准(DC chart)来确定。

另外请教一下怎么能判定,PLL2锁定? ------ 通过配置寄存器,将PLL2的 锁定标志 输出。

你的接口通讯有异常吗?------ 我没有试验过 读回功能。

你好 请问CODELOADER的LE脚 我刚才看了一下为什么一直是低电平,这样可以吗

还没有通讯,刚才用逻辑分析仪抓了一下时序,发现那个LE脚一直都是低电平,不知道这样可不可以配置

不可以

不妨参见DATASHEET里的编程时序图

好的,谢谢。另外,请问有什么现象让我可以确定PLL2锁定了?

唯一能确定 PLL2锁定的标志,就是 PLL2 DLD。将 PLL2 DLD引出,用示波器直接测量观看。

谢谢,现在PLL2 DLD输出的是高电平,输出频率跟设置的也相同,应该是锁定了。