DP83848C以太网PHY芯片配置问题

时间:10-02

整理:3721RD

点击:

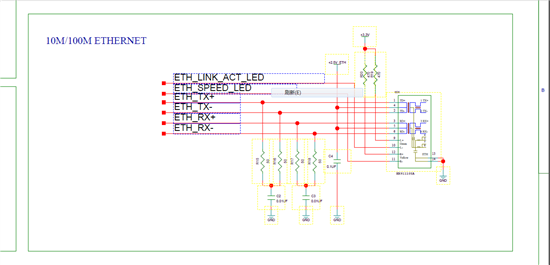

大家好!这边使用STM32F407+DP83848C构建了100M以太网电路,在用ST提供的TCP echo server例程进行网络测试时,MCU发现下载完程序,使用命令窗口发送数据时,可以正常接收,断电后重新上电,发送数据时提示为超时,使用硬件复位PHY,按下连接到PHY芯片Reset_N管脚的按钮后,又可以正常发送接收数据,这边想得是不是上电时没有满足PHY的上电时序?请问有人碰到过这个情况吗?电路图详见附件

DP83848C内部集成了POR(power on reset)电路,所以上电时序应该是没有问题的,应该是中断机制没有做好,断电时应该先发送一个中断指令,表示发送中断,否则重新上电之后可能就会出现发送超时的现象。

谢谢您的回复,但是我用开发板跑同样的程序时,重新上电之后不会出现问题,查看PHY芯片数据手册,发现上电复位后PHY需要至少167ms的延时,才把锁存引脚电平,配置PHY的工作状态,而硬件reset后,只需要3us的时间就可以配置完成,所以感觉是上电之后,MCU载入程序完成,企图与PHY之间建立连接,可以PHY还没有配置完成,所以修改程序,在MCU初始化网络之前,加入200ms的延时,烧写程序,重新上电后,网络可以正常收发数据,现在的问题是为什么开发板不延时也可以通信,而设计的板子需要增加延时呢?下图是开发板PHY与RJ-45的连接图,附件是MCU与PHY的连接图