关于时钟芯片CDCM7005锁定问题

时间:10-02

整理:3721RD

点击:

中秋快乐!

我遇到的问题是这样的,第一块电路板采用温补晶振作为CDCM7005参考时钟,时钟频率60MHz,亚控晶振120MHz,环路滤波器采用手册默认参数,经过参数调整,鉴相频率1.2MHz,模拟锁相模式,PFD pulse width delay 1.5ns,电荷泵电流1.6mA, cycle number 256,检测窗口8.5ns。这组参数在该电路板能让PLL_LOCK信号变为高。

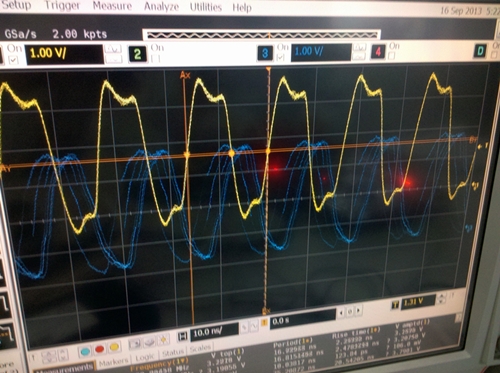

第二块电路板接收第一块电路板由FPGA产生的60MHz时钟,首先时钟在第一块电路板经过转换为LVDS信号经过同轴电缆传输,第二块电路板接收到LVDS时钟后再转换为单端信号输入到CDCM7005的参考时钟,第二块电路板CDCM7005电路为模拟锁相模式,压控晶振120MHz,环路滤波器采用手册默认参数,若采取第一块电路板锁定的参数,它是不能锁定的。经过参数调整,能先让PLL_LOCK信号为高,但测量参考时钟与CDCM7005输出时钟相位不是固定的,示波器波形如下,不知道为什么?

此外,我调节锁相环参数过程中,有些参数会让PLL_LOCK信号产生震荡,有的参数让PLL_lock信号产生一个尖峰脉冲后锁定,这个与芯片手册中说的模拟锁相模式下PLL_LOCK经过一个单调的过程锁定不太一致,请给与解答?谢谢

是否蓝色为第二块板的输出,

你调整什么参数后第二块板锁定?第二块板看上去抖动很大,请把监相频率提高看下效果