寻求产生30.4MHz时钟的方案设计

时间:10-02

整理:3721RD

点击:

大家好!我需要产生30.4MHz的时钟,对时钟要求是频偏和相噪指标都得很好。因为没有高精度30.4MHZ的晶振,现拟采用10MHZ 的OCXO,经过LMX2581倍频到60.8MHz后再二分频降到30.4MHz,不知道这样行不行?请问大家能帮忙提供一个解决方案吗?

可以直接用LMK03000,03001,03033等芯片。10MH输入,30.4M输出

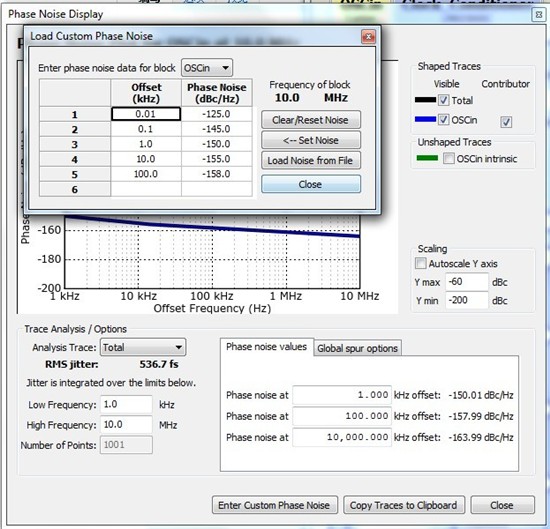

我拟采用的10MHz晶振是O32A-R326 10.00MHz,频率牵引范围为:±0.5ppm~±0.8ppm;

相位噪声:10Hz -125dBc/Hz

100Hz -145dBc/Hz

1kHz -150dBc/Hz

10kHz -155dBc/Hz

100kHz -158dBc/Hz

如果采用上面的芯片,时钟性能指标能达到什么程度?

clock design tools里面可以仿真。你上网可以免费下载

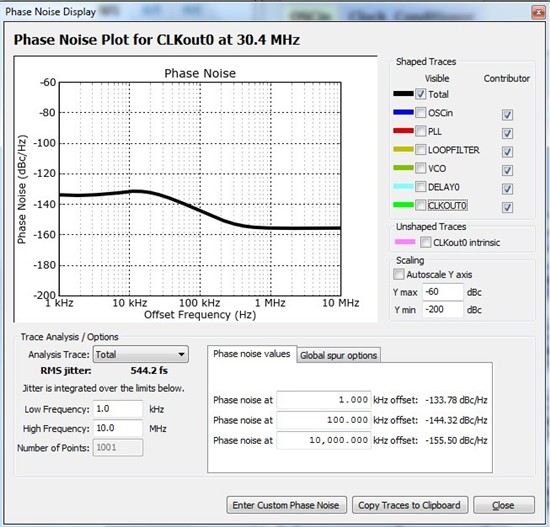

您好,可以通过TI的Clock Design Tool进行相应的仿真。可以手动输入晶振的噪声得到相应的仿真结果。下图是我设置以及仿真的结果(采用的是LMK03000C)