高速采集系统中的时钟

时间:10-02

整理:3721RD

点击:

高速数据采集系统中的时钟很重要,为什么,能说说理由吗?

在高速数据采集系统中对信号进行高分辨率的数字化处理需要谨慎的选择时钟,才不至于使其影响模数转换器(ADC)的性能。

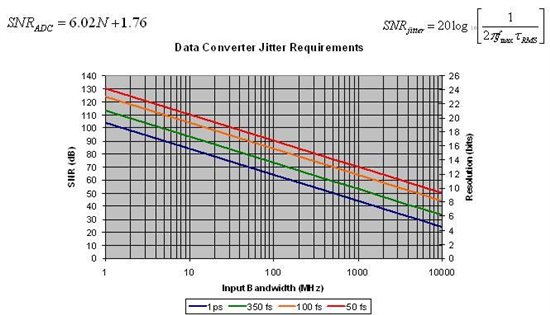

高速数据采集系统,主要关注时钟的相位噪声和杂散。如果相位噪声过大,简单理解造成AD采样周期的不匀均。也就是ADC的实际定时位置与其理想定时位置产生偏差。这称之为时钟的抖动。时钟的抖动会使ADC引入噪声。从而成ADC的SNR下降。具体关系,有相关公式可以表示出jitter对SNR的影响。

主要在ADC采集数据的有效位跟采样数据的一致性上有影响。时钟抖动会降低ADC信噪比,减少采集有效位;时钟偏移导致采样的起始点差异,影响数据一致性。

SNR=-20*log(2*pi*Fin*Jitter)

SNR就是ADC的主要指标之一。Jitter是时钟的指标之一。

所以很重要

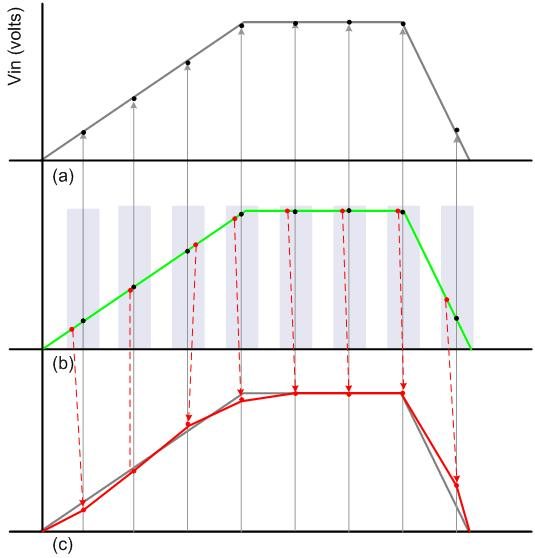

上张图片给你直观的说明: Distortion in a sampled waveform;一个理想的时钟抖动后采样到的信号就会有一定的Distortion

理想ADC的信噪比与有时钟抖动后的信噪比可以看出;采样的频率越高,bit位数越高对时钟要求越高;