LVDS热备

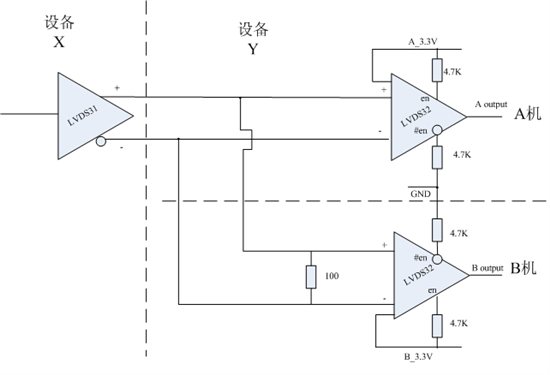

在设计中,我设计了TI公司LVDS双热接收(设备Y),具体如下图所示。A机、B机独立供电,但共地。且除了LVDS接口在差分端连接外,A、B机其它地方没有信号相连。

功能描述:设备X通过LVDS31发送信号给设备Y。设备Y中A机、B机都开机,分别接收设备X发送过来 数据,并进行独立处理。

问题:在调试过程中发现,只开A机,A机电流0.556A(举例);只开B机0.33A(举例)。

将A机、B机都上电,发现A机电流为0.495A,B机0.21A。

请问这是出了什么问题?下图连接是否有可以?该如何解决。谢谢。

请高人指点,TI技术支持请支持

补充:X设备使用SN55LVDS31W,Y设备使用SN55LVDS32W,都是TI公司匹配产品

1. 单A/单B/A+B这三种测试条件下功能是否正常?Y设备是否都能够正确接收来自X设备的数据?

2. X设备的手册上是否有LVDS输出口的用法?是否能直接直流耦合到一个100 Ohm的负载上?会不会是两个接口之间存在着不匹配的问题?

谢谢回复,

1.三种测试条件下,功能均正常,即LVDS32都能正确接收X设备的数据;

2.X设备为TI公司LVDS31发送数据,Y设备为TI公司LVDS32,配对使用。不存在不匹配的情况。

补充,X设备使用SN55LVDS31W,Y设备使用SN55LVDS32W,都是TI公司匹配产品

手册上有写这两颗芯片的工作电流在几十个mA,按说在功能正确的情况下不太可能跑到几百mA的量级。可否把你的电路图发上来?最好能把测试用的框图也发上来,以便评估

这项目是公司的,不让带到网络上。有FPGA,SRAM,FLASH等,8颗LVDS32,4颗LVDS31.测试用部分接上是验证功能是否正常,下面的测试是基于没有测试部分的数据。

A机、B机在原理上完全相同。在排除问题时,保留A机所有LVDS32,然后:(1)我将B机的所有LVDS32、LVDS31拆除,(2)在B机焊接一颗LVDS32.(3)在B机焊接两颗LVDS32.

在(1)中,A机单独开,或者B机单独开,与A机B 机同时开,电流一致(数据在公司,没带回来)。

在(2)中,就出现了最开始描述的电流变化,只开A机,A机电流0.556A(举例);只开B机0.33A(举例)。

将A机、B机都上电,发现A机电流为0.495A,B机0.21A。

在(3)中,只开A机,A机电流0。556;只开B机0.413;同时开A、B机,A机电流0.445,B机

根据调试发现的现象,大概是在B机增加一个LVDS32,同时开机时,A机电流就会下落0.05A左右.

要是方便的话,可以Call我,叶 tel:18221864768,非常感谢

(2)A8B0=0.556A,B1A0=0.33A,A8B1=0.495A,B1A8=0.21A。等于说A机少了60mA,平均每颗SN32少了8mA;B机少了120mA,平均一颗SN32少120mA。

(3)等于说A机少了111mA,平均每颗少了14mA;B机少了多少没测。

两个疑问

1. B机增加了一个SN32,但是单开时电流增加了0.413-0.33=83mA,不太正常。从手册上看,一颗SN32烧的电流最多也就是18mA,剩下的65mA是哪里多出来的?会不会是因为多了一路SN32,所以后级的FPGA因为多处理一路数据,所以多烧了65mA?

2. 只有Y设备的电流测试数据,没有X设备的。你测一下三种情况下X设备的电流。

单位不能上网,痛苦。。。。

今天回来的匆忙,没将测试数据带回来。目前想确认以下问题:

1)我这种应用是否可行可靠;

2)有否存在潜通路问题。

补充:当A机、B机所有电路都完整时,即(B机8颗LVDS32,4颗LVDS31都工作)。

A机单独开,电流0.5A左右,

B机单独开,电流0.6左右。

A机、B机一起开,A、B机电流各为0.13A左右

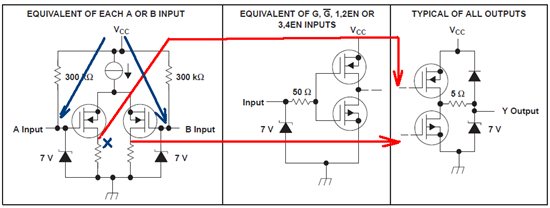

1. 对照SN32手册上图5,图8,图9再查一下,看看是不是有电流在B机Power down的时候从SN32漏过去了。

2. 如果怀疑单开一个时有电流泄露的通路,可以在测试的时候看一下X机的电流。看看单开时X机电流多大,两个都开时X机电流又是多大。

经过测试:

1.在B关机的时候,B机的VCC和GND电压仅有0.1V以下,

但经测量,发现存在如下现象:

A机关,B开时,B机单片LVDS32的电流为78mA(LVDS32无输入);

A机关,B开时,B机单片LVDS32的电流为13.5mA(LVDS32有输入,且输出正确);

A机开,B开时,B机单片LVDS32的电流为60mA(LVDS32无输入);

也就是说,这种连接方式与我的输入状态有很大关系。请问这是什么情况?

考虑手册第四页等效输入输出的图,如果B机无输入,那么B机的输入端应该是维持在高电平,或者说,约等于VCC,只有小部分电流通过高阻通路泄放掉。此时等效输入电路X点的电平约等于GND,少量电流从VCC通过几乎被关断的电流源流过两个电阻。再看输出端,输出端的PMOS和NMOS此时看到的是两个低电平,所以上管PMOS会打开,造成的结果是一路直流电流从上管向负载泄放。

当A,B都开但是没有输入时,A,B的等效输入端看到的电阻是两个300K的并联,就是150K,等于说电阻减小了,泄露会增大一些,这样X点的电平会上移一些,造成的结果是输出端上管PMOS的电流比之前减小一些。

当有输入时,不管哪个机器打开,其等效输入端看到的是动态变化的输入,从而等效输出端会动态的向负载抽/灌电流,此时平均电流会很小。

以上分析皆假设等效输出Y output后面都有一个并不是很大的阻性负载。