几个关于CDCM7005的问题

1.如何立即下面数据手册中下面这句话:The PFD pulse width delay gets around the dead zone of the PFD transfer function and reduces phase noise and reference spurs.“PFD pulse width delay”是将脉宽变宽还是如何?

2,.Cycle slip occurs when the phase shift at the PFD is greater than one period of the frequency. It is a complete (integer number) cycle jump,这里的相移大于一个时钟周期对哪个时钟来讲?能否有一个时序图来说明下。

3.鉴相器的复频域模型在官方给的软件中是Ip/2pi,是怎么得到的呢?

谢谢!

以下是个人见解,如有不当敬请指出。

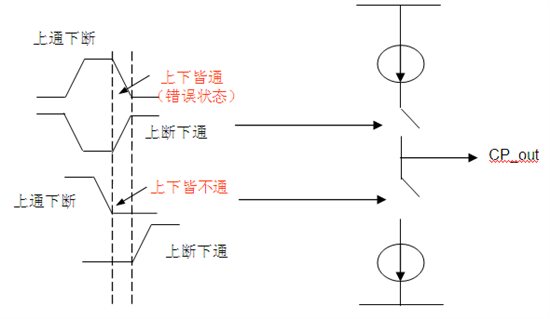

1. get around意思是规避,逃避。这句话的意思应该是用来控制CP输出电流开关的脉冲信号,通过时间上的延时确保CP上下两路电流开关不会同时导通,规避由此带来的spur和Phase Noise。

2. Cycle slip即周期滑移,是指反馈回PFD的信号在相位上落后reference信号一周期,这个周期是PFD周期,1/Fpfd (=Fref/R)。我们通常认为经过PFD + CP + VCO + divider后,反馈回来的信号在相位上会落后于reference,此时通过环路的调整,反馈信号频率升高,开始在相位上“追赶”reference信号,并最终和reference信号达到同相。但是当环路带宽很小时,反馈信号要通过较长的时间反馈回PFD,这样造成的结果是反馈信号的相位越来越落后于reference相位,最终当相位差为一个PFD周期时,两信号同相,PLL稳定。直观理解是两个运动员跑步,落后的一方要尽力追赶才能与超前的一方相遇,否则超前的一方会在“多跑一圈”后与落后的一方相遇。周期滑移并不影响稳态时的spur和phase noise性能,但会增大PLL的稳定时间。

3. PLL并不是一个纯粹的连续时间系统,PFD+CP严格意义上是一个离散系统。通过PFD的控制,CP会不断地做充电和放电的动作,也就是说,充电和放电在时间上看是离散的。但是当环路带宽小于1/20~1/10 Fpfd时,可以把这部分电路看成一个连续系统。直观的理解就是在一个较长的时间内,尽管充电和放电时间不同,但是平均的充电电流(或说放电电流)等于Icp/2pi。关于这个问题更为详尽的解释,请参见Behzad Razavi写的《RF Microelectronics》一书。

4. 一般来说,PLL芯片都会集成Cycle slipping cancellation电路,用来消除周期滑移,使PLL加速稳定。如果没有这部分电路,则建议

Fpfd = (10~50) * BW

其中Fpfd是鉴相频率,BW是PLL闭环带宽。若倍数太小,则不满足连续系统近似条件,phase noise和spur性能差。若倍数太大,有可能造成周期滑移。