高速ADC 技术咨询:: ADS54J20

时间:10-02

整理:3721RD

点击:

Hi 各位专家

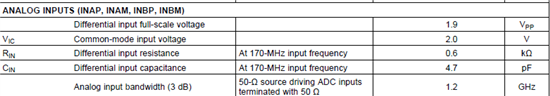

我这边有个新项目考虑用TI的ADS54J20,这是一颗1GSPS采样率的双通道ADC。它的模拟接口的内部阻抗为单端600欧姆,差分1.2K欧姆。

根据它的EVM板资料,建议的是前端采用50或100欧姆差分端接匹配,即在ADC模拟输入端放一个50或100欧姆电阻进行端接匹配,也就意味着前方的模拟驱动电路都是50或100欧姆的阻抗端接。这样做,满幅度接收条件下,ADC前端的接收功率为19dBm,而进入ADC的信号功率为4dBm。

能否在ADC的前端,采用升压网络,将阻抗匹配到ADC的1.2K欧姆的内阻上?这样,可以大幅度减小ADC前端的信号功率,前方运放的增益幅度可以减小,阻抗匹配的要求也可以满足。

可能想得简单了, 这个 50 欧姆是为了匹配信号传输线的阻抗的. 采用升压网络后, 阻抗变化, 你的传输线的阻抗也要跟着变么?

可以适当的提高,但是不能无限制的。有多种因数的

以前的高速ADC的推荐过200欧姆的匹配。

采用两个600ohm的电阻使得输入信号的共模电压偏置到Vcm。

而对于ADC的差分输入端来说,输入阻抗是50ohm,和前端50ohm信号源匹配。