关于DP83822 RESET管脚使用?

时间:10-02

整理:3721RD

点击:

您好,

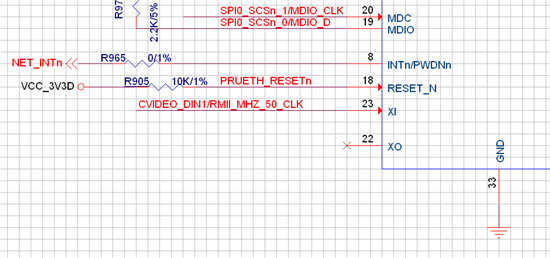

1)DP83822第19脚RESET管脚上拉有问题没?

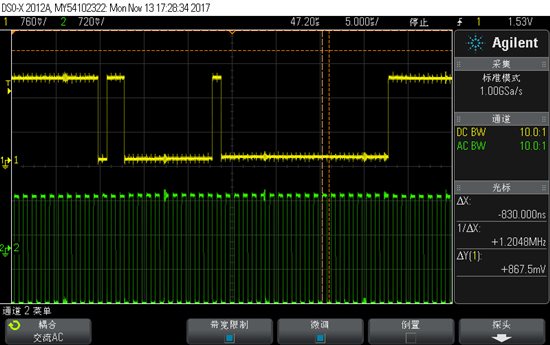

2)DSP通过MDIO读取DP83822寄存器的数据全为0,MDC有时钟信号,不知道问题在哪里?

谢谢,

下面是示波器截图,上面是数据,下面是时钟;

1) RESET_N上拉是没问题的。但是最优化情况下是RESET_N接到MCU的GPIO引脚上,如果出现一些意想不到的情况,还可以使用硬件复位功能。

2) 优先查看PHY的地址是否设置正确,因为DP83822的strap支持4个模式,有时候会分不清,优先确认地址和MDIO的地址是否一致。

还是不建议reset直接上拉,因为尽量上掉电保证时序正常。

上电过程中,当VCC上电起来到稳定之后,建议再将reset拉高。

同样,掉电过程,建议先将reset先由高到低,然后再掉电。

因此最好是通过GPIO来控制上掉电的时序。