ADS8555 busy信号响应正常,但数据全为0的问题

时间:10-02

整理:3721RD

点击:

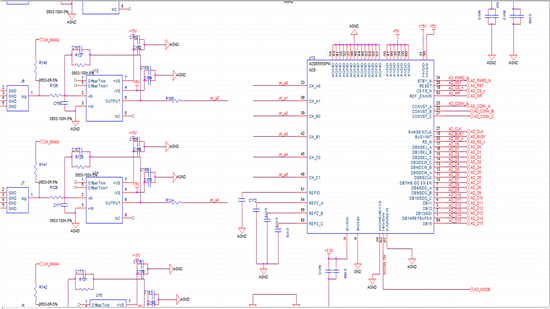

我使用ADS8555 电路接参考设计的,采用并行,硬件模式。前端运放用的opA627,HVDD HVSS 为15V -15V。BVDD = 3.3V。

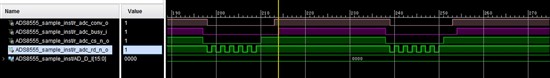

在芯片复位后,给convert信号之后,busy信号有变高保持,后变低的过程,但读出的数据全为0,我给的输入信号为1.8V,3.3V时都一样。

测到VREFio = 2.5V VrefA = 2.5V,Vref B = 1.8V, Vref C=2.5V。C通道没有使用,悬空的,但在C通信管脚上,pin45 pin48测到3.3V电平。

以为是芯片坏了,换了一颗后,一样的情况。

Hi heng,

请问时序逻辑图里边一个时间格对应的实际时间是多少呢?

50ns.

已解决,数据正常了。原因是硬件工程师把原理图封装画错了,导致40.41 AVDD 与AGND短路。

将芯片pin40 pin41挑起来,飞线到35,36AVDD上再正常。看来要改板了。

(不过有点奇怪,电源短路了也没见我板上总电源变大,5V也没拉跨)。

谢谢@willing 回复。