ΣΔADC中数字滤波器设计疑问

时间:10-02

整理:3721RD

点击:

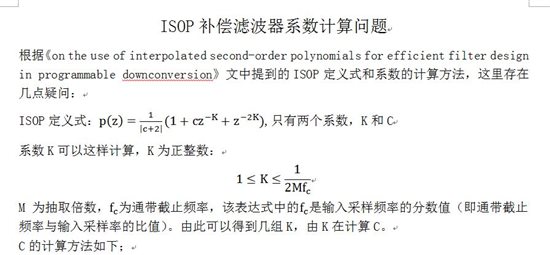

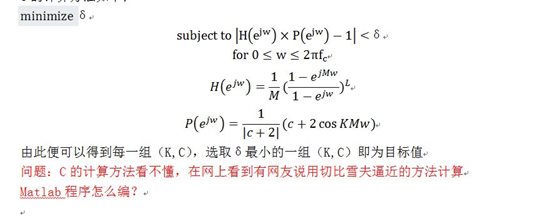

本人在做一款多速率数字滤波器,用于ΣΔADC,第一级使用4阶CIC滤波器实现相应的抽取倍数,但是通带也一定的衰减,因此我在第二级使用补偿滤波器来补偿通带的衰减,常用的方法是升幅FIR滤波器,不过我查阅论文时发现了一种利用内插二阶多项式的方法来补偿通带衰减,但是对论文中提到的相关参数的计算有些看不懂,因此希望能有人为我解答疑惑,问题描述如下,论文放在附件中,有兴趣的朋友可以下载看看

一个简单问题, 好象越扯越远了.

无意去研究你的论文细节. 采用升幅FIR滤波器来补偿通带衰减,肯定是可行的

首先谢谢你的回复,升幅FIR已经做出来了,不过我感觉阶数有点高,耗费的资源有点多,就想用ISOP的方法去补偿通带衰减,这个资源方面已经要省不少