ADS1263实际数据输出率与理论配置相差较大

时间:10-02

整理:3721RD

点击:

你好,恒荣幸你能够在百忙之中查阅我的帖子,在此表示我诚挚的谢意。

本人在设计ADS1263 数据采集卡时遇到ADC实际数据输出率与理论配置不符的情况。具体细节如下。

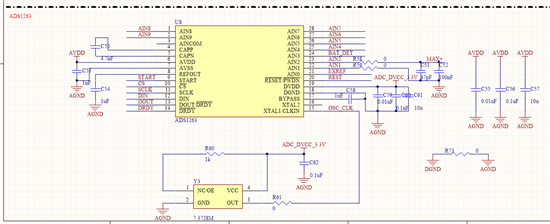

ADS1263拓扑电路参考数据手册,设计如图 1 ADS1263电路原理图所示

图 1 ADS1263电路原理图

在实际测试中发现,将ADS1263配置为连续转换模式,通过ADS1263的DRDY引脚触发STM32F407外部中断从而读取ADC1的数据。

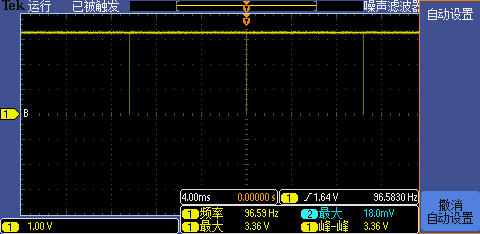

1、 当数据输出速率配置为100sps以内时实际数据输出速率(通过示波器测量DRDY引脚)与理论配置的数据输出速率相差不大。如图 2配置为100sps时RDRY脚输出波形所示,实际测量DRDY输出速率为96.58Hz

图 2配置为100sps时RDRY脚输出波形

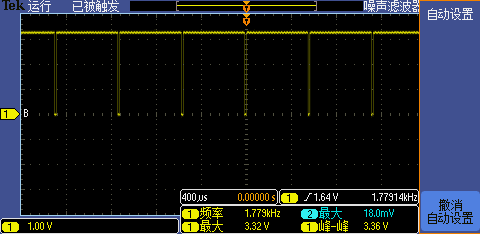

2、 当数据输出速率配置较高时实际数据输出速率明显小于理论值。如图 3 配置为4800sps时RDRY脚输出波形所示为理论配置为4800sps数据输出率,但是实测DRDY引脚的频率为1.779k与理论值相差较大。

图 3 配置为4800sps时RDRY脚输出波形

另外已经用示波器实测晶振输出频率为7.4MHz左右,也已经确定ADC的寄存器已经正确写入到ADC(配置以后STM32读取ADC相应的寄存器发现输出速率的寄存器已经正确配置)

请问主要是什么原因导致ADC实际的输出速率与理论配置的速率相差较大的了?

再次感谢你的指导。

离最高频率 38.4K 还相去甚远, 所以感觉还是设置方面的问题 可能性大

再验证一下时序波形, 看看有没有问题

老哥求1263的F4驱动!