LM98640 输出LVDS数据采集问题

时间:10-02

整理:3721RD

点击:

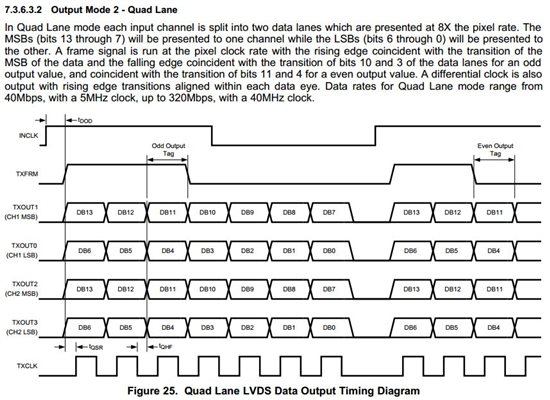

自制FPGA数据采集板,通过txtfrm和txtclk采集输出LVDS数据,怎么有错,因为输出时钟是个假320MHz(INCLK=40MHz),每个点只有7个时钟,差一个,到底按照什么时序采集才能正确实现串转并?

好象没有太看明白你的问题, 如何是假信号了呢? 手册给出了时序了呀

就是按照txtfrm和txtclk的时序来采集的,选取上升沿,结果不对,

请问您解决了吗,我遇到了一样的问题

可以加qq好友吗,我们一起讨论一下。我的qq是296758762

请问您用过这个芯片吗。

没有解决

用过

看我qq,我们加下好友,一起解决

实际datasheet中的时序,如上图也是7个clock,7个clock之后,实际输出的是low。没有问题。

只用TxFrm和Txclk上升沿来判断么?

另外问下,这款产品的DNL测试给个过满度正弦波测试全码,通过码字概率分布计算怎么会出现两头分别有一坨很大的值?方法有问题么?

您有联系方式么?我可以电话或者邮件咨询下么?谢谢。