ADC344X的外部同步输入问题

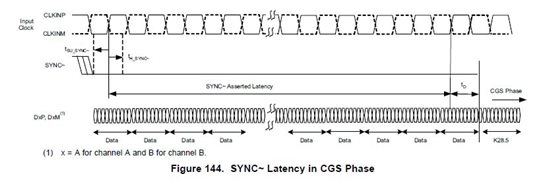

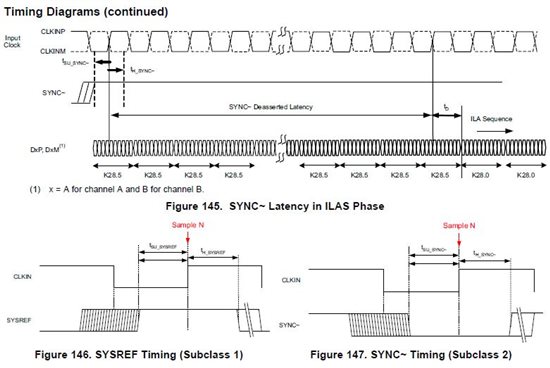

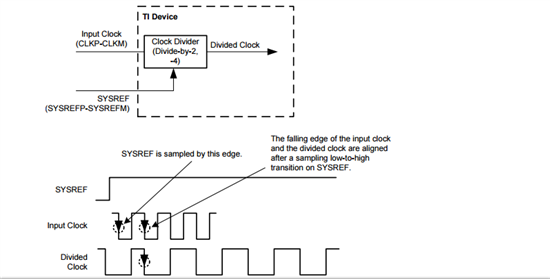

您好,我查询到ADC344X的外部同步输入SYSREF范围是-0.3~(AVDD + 0.3 = 2.1)V,请问是否可以通过FPGA输出1.8V信号来直接驱动?另外,ADC344X的手册上并无SYSREF时序图,可否参考同系列adc32j44的SYSREF时序图进行设计(即仅提供一个上升沿或下降沿SYSREF时钟即可完成4通道ADC同步?)?如下图所示

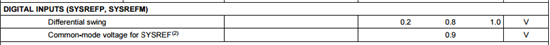

关于SYSREF的电压范围,请参考,也就是说0.9V的共模电压,如果最大1V的swing的话,那么它的电压范围就是0.4V~1.4V。

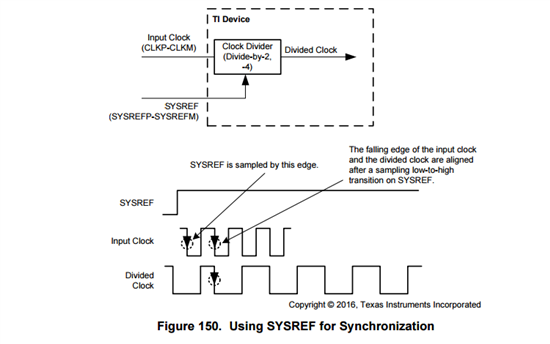

SYSREF是用来reset内部divider电路,保证divider出来的时钟相位同步,时序图可参考datasheet Figure150.建立和保持时间datasheet中也有列出。

非常感谢Kailyn Chen女士的回答,原来数据手册已经更新。另外,我还想请教一下,

①手册中说“When multiple ADC344x devices are onboard and the clock divider option is used, the phase of the divided clock among the devices may not be the same. The phase of the divided clock in each device can be synchronized to the common sampling clock by using”,是否意味着只使用一片ADC344X的四通道进行数据转换时,且不使用分频功能时,无需考虑同步问题?

②只使用一片ADC344X的四通道进行数据转换时,若使用分频功能时,是否需要考虑四通道间的同步问题?

③SYSREF的输入,除使用特定时钟管理芯片提供SYSREF OUT外,有无简化设方案?即利用FPGA引脚直接提供SYSREF OUT给ADC344x?

感谢您的回答,谢谢

考虑的时钟相位同步只是指的图中的input clock分频后的divided clock,跟四路ADC没有关系,因此只有当多个ADC344x级联的时候,才会考虑多个divided clock的相位同步。

对于SYSREF的输入,除了用单独的时钟芯片之外,如果FPGA输出也可以,但要保证满足幅值范围,0.9V的共模,0.8~1V的swing。

谢谢您的耐心解答