ADS1274使用SPI读取的问题

请教各位,我用ADS1274的SPI方式读取,ADS1274使用高分辨率模式,数据输出为TDM动态方式,4通道全开启。SCLK/FCLK = 1,MCU的SPI的SCLK空闲状态为低电平,采用8位帧结构。

MCU采用外部中断来接收DRDY下降沿信号,当DRDY信号下降沿来时进入中断,进入中断后先等待1个tclk,即上图中“tDS”,然后开启SPI,SPI每接收到1个字节就产生接收中断,接收中断将读到的这1个字节赋值到一个数组中,连续读取12个字节后关闭SPI(我试过让SCLK一直运行,也就是说不在外部中断中开启和关闭SPI,但是不管是高采样率还是低采样率,读到的数据直接是错误的)。

现在的情况是,当我的SCLK和FCLK都为656.25 KHZ(采样率1281SPS)时,数据读取很准确(1281×12 个字节)。但是当SCLK和FCLK都为1.3125 MHZ(采样率2563SPS)或以上时,读到的数据就开始丢了很多。

用示波器测量:

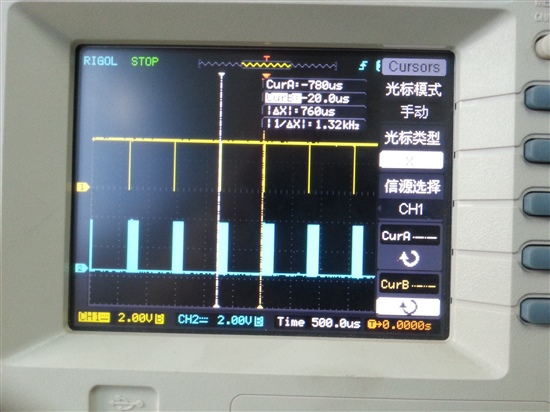

当SCLK和FCLK都为656.25 KHZ时的DRDY的波形正常,如下图,黄色为DRDY,蓝色为SCLK:

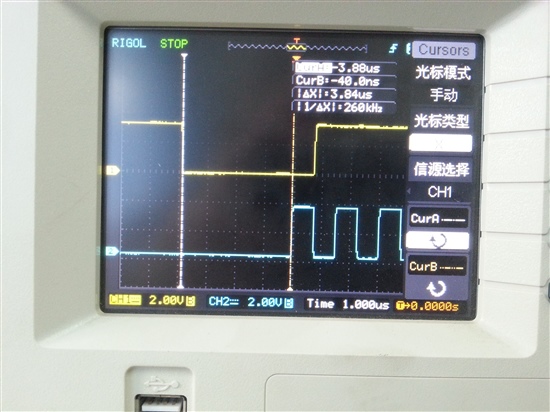

“tDS”也正常,如下图,黄色为DRDY,蓝色为SCLK:

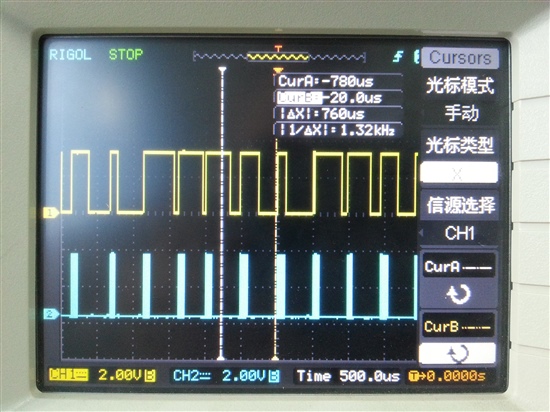

当SCLK和FCLK都为1.3125 MHZ时的DRDY波形就不正常了,如下图,黄色为DRDY,蓝色为SCLK:

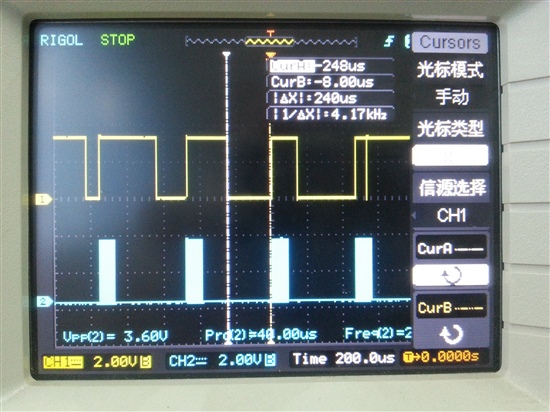

“tDS”也变得不正常,如下图,黄色为DRDY,蓝色为SCLK:

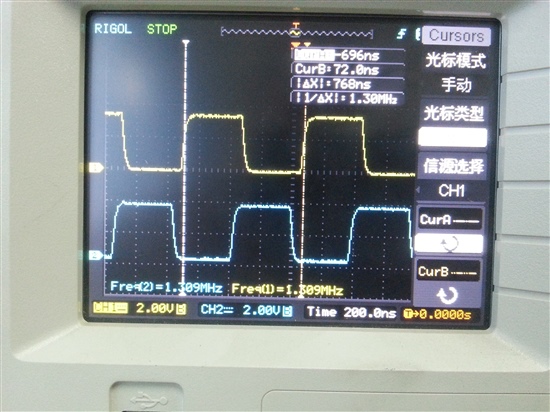

SCLK和FCLK都正常,如下图,黄色为FCLK,蓝色为SCLK:

请问,我该如何改进才能消除以上DRDY信号不正常的问题呢?

问题找到了,是操作系统的任务调度时间太长。

- 提高SCLK和FCLK的频率后,数据异常,有可能的一个原因是SPI走线的阻抗没有做好,可以用示波器抓一下波形

Terry_Chen

- 提高SCLK和FCLK的频率后,数据异常,有可能的一个原因是SPI走线的阻抗没有做好,可以用示波器抓一下波形

你好,我发现是DRDY信号不正常的原因,请问这是怎么回事呢?