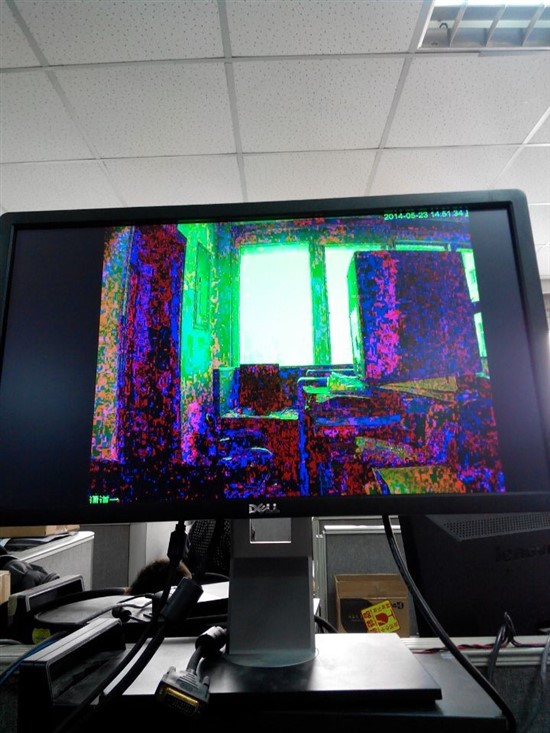

THS8200输出图像不是全屏且失真

输入格式是bt1120 720P@50 采用如下配置,应该是推荐的配置吧,自己不清楚

//THS8200

WR_REG,THS8200,0x01,0x03,0x01 // chip_ctl

//CSC bypassed in THS8200

WR_REG,THS8200,0x01,0x16,0x00 // csc_offset1

WR_REG,THS8200,0x01,0x17,0x08 // csc_offset12

WR_REG,THS8200,0x01,0x18,0x02 // csc_offset23

WR_REG,THS8200,0x01,0x19,0x03 // csc_offset3

WR_REG,THS8200,0x01,0x1C,0x43 // dman_cntl

//Sync level setup

WR_REG,THS8200,0x01,0x1D,0x00 // dtg_y_sync1

WR_REG,THS8200,0x01,0x1E,0x49 // dtg_y_sync2

WR_REG,THS8200,0x01,0x1F,0xB6 // dtg_y_sync3

WR_REG,THS8200,0x01,0x20,0x00 // dtg_cbcr_sync1

WR_REG,THS8200,0x01,0x21,0x00 // dtg_cbcr_sync2

WR_REG,THS8200,0x01,0x22,0x00 // dtg_cbcr_sync3

WR_REG,THS8200,0x01,0x23,0x23 // dtg_y_sync_upper

WR_REG,THS8200,0x01,0x24,0x2A // dtg_cbcr_sync_upper

WR_REG,THS8200,0x01,0x25,0x28 // dtg_spec_a

WR_REG,THS8200,0x01,0x26,0x6E // dtg_spec_b

WR_REG,THS8200,0x01,0x27,0x28 // dtg_spec_c

WR_REG,THS8200,0x01,0x28,0x04 // dtg_spec_d

WR_REG,THS8200,0x01,0x29,0x00 // dtg_spec_d1

WR_REG,THS8200,0x01,0x2A,0x04 // dtg_spec_e

WR_REG,THS8200,0x01,0x2B,0xC0 // dtg_spec_h_msb

WR_REG,THS8200,0x01,0x2C,0x00 // dtg_spec_h_lsb

WR_REG,THS8200,0x01,0x2D,0x00 // dtg_spec_i_msb

WR_REG,THS8200,0x01,0x2E,0x00 // dtg_spec_i_lsb

WR_REG,THS8200,0x01,0x2F,0x6E // dtg_spec_k_lsb

WR_REG,THS8200,0x01,0x30,0x00 // dtg_spec_k_msb

WR_REG,THS8200,0x01,0x31,0x00 // dtg_spec_k1

WR_REG,THS8200,0x01,0x32,0x00 // dtg_speg_g_lsb

WR_REG,THS8200,0x01,0x33,0x00 // dtg_speg_g_msb

WR_REG,THS8200,0x01,0x34,0x06 // dtg_total_pixel_msb

WR_REG,THS8200,0x01,0x35,0x72 // dtg_total_pixel_lsb

WR_REG,THS8200,0x01,0x36,0x00 // dtg_linecnt_msb

WR_REG,THS8200,0x01,0x37,0x01 // dtg_linecnt_lsb

WR_REG,THS8200,0x01,0x38,0x82 // dtg_mode

WR_REG,THS8200,0x01,0x39,0x27 // dtg_frame_field_msb

WR_REG,THS8200,0x01,0x3A,0xEE // dtg_frame_size_lsb

WR_REG,THS8200,0x01,0x3B,0xFF // dtg_field_size_lsb

//CSM Map 601 to 0-1023 DAC output

WR_REG,THS8200,0x01,0x41,0x40 // csm_clip_gy_low

WR_REG,THS8200,0x01,0x42,0x40 // csm_clip_bcb_low

WR_REG,THS8200,0x01,0x43,0x40 // csm_clip_rcr_low

WR_REG,THS8200,0x01,0x44,0x53 // csm_clip_gy_high

WR_REG,THS8200,0x01,0x45,0x3F // csm_clip_bcb_high

WR_REG,THS8200,0x01,0x46,0x3F // csm_clip_rcr_high

WR_REG,THS8200,0x01,0x47,0x40 // csm_shift_gy

WR_REG,THS8200,0x01,0x48,0x40 // csm_shift_bcb

WR_REG,THS8200,0x01,0x49,0x40 // csm_shift_rcr

WR_REG,THS8200,0x01,0x4A,0xFC // csm_mult_gy_msb

WR_REG,THS8200,0x01,0x4B,0x44 // csm_mult_bcb_rcr_msb

WR_REG,THS8200,0x01,0x4C,0xAC // csm_mult_gy_lsb

WR_REG,THS8200,0x01,0x4D,0x91 // csm_mult_bcb_lsb

WR_REG,THS8200,0x01,0x4E,0x91 // csm_mult_rcr_lsb

WR_REG,THS8200,0x01,0x4F,0xFF // csm_mode

WR_REG,THS8200,0x01,0x70,0x28 // dtg_hlength_lsb

WR_REG,THS8200,0x01,0x71,0x06 // dtg_hdly_msb

WR_REG,THS8200,0x01,0x72,0x71 // dtg_hdly_lsb

WR_REG,THS8200,0x01,0x73,0x06 // dtg_vlength_lsb

WR_REG,THS8200,0x01,0x74,0x00 // dtg_vdly_msb

WR_REG,THS8200,0x01,0x75,0x01 // dtg_vdly_lsb

WR_REG,THS8200,0x01,0x76,0x00 // dtg_vlength2_lsb

WR_REG,THS8200,0x01,0x77,0x07 // dtg_vdly2_msb

WR_REG,THS8200,0x01,0x78,0xFF // dtg_vdly2_lsb

WR_REG,THS8200,0x01,0x79,0x00 // dtg_hs_in_dly_msb

WR_REG,THS8200,0x01,0x7A,0xA2 // dtg_hs_in_dly_lsb

WR_REG,THS8200,0x01,0x7B,0x00 // dtg_vs_in_dly_msb

WR_REG,THS8200,0x01,0x7C,0x05 // dtg_vs_in_dly_lsb

WR_REG,THS8200,0x01,0x82,0x3B // pol_cntl

WR_REG,THS8200,0x01,0x83,0x00 // cgms_header

WR_REG,THS8200,0x01,0x84,0x00 // cgms_payload_msb

WR_REG,THS8200,0x01,0x85,0x00 // cgms_payload_lsb

由上面的图片可以看出视频图像没有全屏,而且图像还花的,colorbar颜色显示正常,但是也没有全屏,不过效果比上面的好。

不知道怎么配置,希望提供帮助或解决思路。

| 这个问题后来解决了吗?我也遇到类似问题? |