AD转换芯片ADS131E08S的采样率问题

时间:10-02

整理:3721RD

点击:

您好!我对 ADS131E08S 这个AD芯片有两个地方存在疑惑。

问题1:

我在ADS131E08S的Datasheet中看到ADS131E08S的采样率可以设置到64kSPS,也是说 1s/64k =15.625us 就可以完成一次A/D转换。

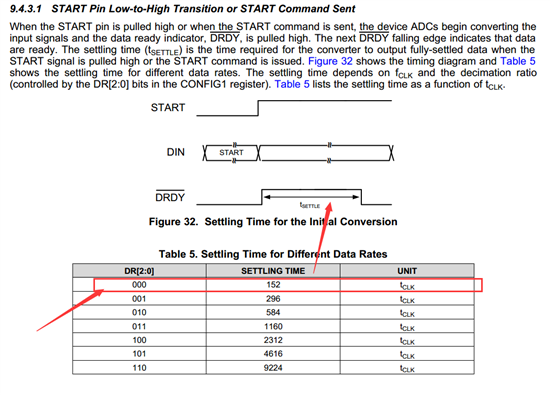

但是在Datasheet中又看到以下的描述:

如果按照这个表格中的关系计数的话:Tsettle = 152*Tclk = 152*444ns = 67.448us ,也就是说每隔 67.448us 才能一次AD转换结果。这个和前面所说的 64kSPS 的采样率不符。

请问 ADS131E08S 从启动AD转换到转换结束到底需要多长的时间?

问题2:

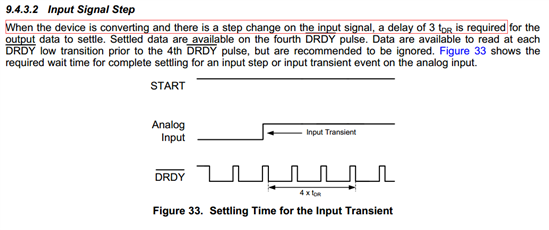

在 ADS131E08S 的datasheet 中有以下描述:

是不是说的这个意思:在AD转换期间,如果模拟输入信号发生了 阶跃变化,那么在发生 阶跃变化后的AD转换的前三个输出是不稳定的,第四个转换结果才是可用的值?

如果是这样的话,那么当输入的模拟信号一直在变化(比如三角波信号)或者输入信号只能保持100us的有效时间那该怎么办?

麻烦各位TI的高手帮回复我一下,急!谢谢!

没有看明白你的时钟是多少, 估计是这个 Tclk 的理解问题了

时钟是2.048MHz ,Tclk在datasheet中也有介绍的,如下

这是个8通道的芯片。每个通道的setting time不一定要小于采样时间。