有关DAC38J84求助TI技术人员

尊敬的各位TI技术支持人员:

您好

以下是我在使用芯片DAC38J84的过程中发现的几个问题以及一些疑惑,希望得到TI技术人员的技术支持:

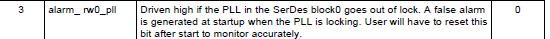

1.在数据手册章节8.3中,第12步,通过alarm_rw0_pll和alarm_rw1_pll来验证SERDES PLL的状态。这两个状态位位于config108的bit3和bit2,在config108的描述中说bit3和bit2会在PLL刚锁住的时候产生错误的alarm,需要用户重置(清零)这两位,然后进行正确的监测。

a.在第12步之前并没有相关重置这两位的操作说明,请问执行该步骤到底如何进行?是先清零config108,然后马上读取congfig108,还是其他操作?

b.请问如何重置这两位?这个寄存器是写清零寄存器,是写1清零还是写0清零?还是写什么清零?如果直接复位整个DA芯片,Alarm相关寄存器会被清零吗?

c.Step 12是否可以不执行,或者放于所有寄存器配置完后再执行,验不验正这两位的状态是否影响DAC的使用?

2.有关alarm的问题

a.有关于config4、config5、config6这三个寄存器是关于alarm_mask的,默认值配置为屏蔽。请问如果屏蔽了alarm会导致什么后果?是我在相关的alarm寄存器(config100-config108)不能读出alarm状态,还是读出的alarm状态是1,还是状态为0,还是DAC输出为0?

b.在config5中bit3和bit2分别是mask alarm from SerDes block 0 PLL lock和mask alarm from SerDes block 1 PLL lock,默认配置为屏蔽。在8.3初始化过程中的step 12 又要求用户去通过alarm_rw0_pll和alarm_rw1_pll来验证SERDES PLL的状态,这不是相互矛盾吗?都屏蔽了还要去验证?并且在step12之前并没有相关操作说要去配置config4、config5、config6,请您给出相关解释及解决方案。

c.我在config4、config5、config6默认配置下去读config108的alarm_rw0_pll和alarm_rw1_pll,读出的都是1,请问在屏蔽状态下应该读出1吗?

d.出现alarm是否会影响DAC输出?还是可以输出,只不过输出是错误的?还是直接输出为0

e.config100-congfig107是不是只可以在TXENABLE为高的时候才可以读?

3.文档中多次提到SIF,请问这是什么的缩写?是串行SPI接口的缩写吗?

4.config30-config32是配置相关的同步信号,请问这个同步是指什么?什么模块和什么模块同步?如何选择,选择不同的方式是受什么影响?

5.DAC38J84的寄存器之间有什么联动的影响?我写10个寄存器再读回来,读回的数值是我写进去的。程序不变,我还是写相同的10个寄存器再读11个,多读一个alarm寄存器(config100-config108中的某一个),就直接导致我前面读回来的值不对了。

以上是我使用过程中遇到的诸多问题,由于网上没有勘误表和其他用户的反馈,我难以解决,希望得到您的有关回复。

问题很多,希望引起TI公司的注意,希望您能为我一一解答与帮助,并向美国总公司进行反映有关该芯片的问题,这是十分重要以及必要的。

祝您,工作顺利,谢谢

应该尽量遵守手册给出的步骤, 除非你反复验证可行, 并在了解其原理后, 从原理上能解释你的操作步骤.

你可以参考一下 DAC3XJ8XEVM 评估模块 (EVM) 给出的软件

http://www.ti.com.cn/tool/cn/dac38j84evm

此问题已在我已在另一贴中已有回复,请查看。转发如下,另外你时钟用的哪个?

1. 在读取状态寄存器的操作一般都是清零再读以确保读取的是当前状态,在手册99页也有对此寄存器操作方法的详细说明。

因此你的问题a.寄存器已经规定读取之前都要重置,即写0再读, 因此无需再赘述了;

b. 请注意文中英文写的是reset this bit意思就是把这个比特清0,即写为默认值0,不可能让你reset this device;

c.为确保正确请按照规范要求执行;

2. a: alarm mask 可以理解为遮蔽报警,是数字逻辑中的一个通用叫法,即此处这个报警不输出到Alarm管脚逻辑,不被寄存器alarm_zeros_txenable_ena和 alarm_zeros_jesd_data_ena用来关闭输出和输入;

b.你理解有误,屏蔽只是屏蔽其输出及其他逻辑使用,但是该状态,他还是在那里;

c.你清0再读还是1的话说明你没有锁定;

d.看是什么alarm, 以及看你是否设置alarm_zeros_txenable_ena和 alarm_zeros_jesd_data_ena, 如果pll有alarm输出一般都不对的;

e.不是

3. SIF是英文serial interface串口的缩写,即此处SPI;

4.在高速数据通信和多天线MIMO应用中同步是一个非常重要的概念,保证了各个数字模块的初始数据和时钟的相位关系;该设置根据同步机制可以选择不同的同步源;如何选择与通信机制和系统方案设计有关;

5. 这要取决于你写了哪些寄存器,读了哪些寄存器,器件工作状态是否改变;

你做的是一个什么项目,可否提供系统框图?前后分别是些什么器件信号,由于该器件的复杂程度,个人建议你先使用EVM;谢谢

谢谢你专业的回复,我现在使用FPGA与DAC做雷达的调频源,目前只是一个学生,没有条件购买EVM.所以遇到诸多问题解决不了