关于ADC32XX时钟配置

你好,最近使用到ADC32XX数据转换器,系统中只使用了一片,且只使用了通道A,50MSPS,14bits的,ADC输出给FPGA,请问,这个ADC的CLKP,CLKM;SYSREFP,SYSREFM该如何配置?是由FPGA产生还是由晶振,频率又是多少?ADC输出的数据同时还有两组信号,DCLK和FCLK,是否都必须接至FPGA,都有什么作用?谢谢。

SYSREFM Negative external SYSREF input

SYSREFP Positive external SYSREF input

如果作为同步源使用, 那么那么也还需要 FPGA 控制.

CLKP.CLKM 作为时钟输入

9.3.2 Clock Input

The device clock inputs can be driven differentially (sine, LVPECL, or LVDS) or single-ended (LVCMOS), with little or no difference in performance between them. The common-mode voltage of the clock inputs is set to 0.95 V using internal 5-kΩ resistors. The self-bias clock inputs of the ADC322x can be driven by the transformer-coupled, sine-wave clock source or by the ac-coupled, LVPECL and LVDS clock sources, as shown in Figure 132, Figure 133, and Figure 134. See Figure 135 for details regarding the internal clock buffer.

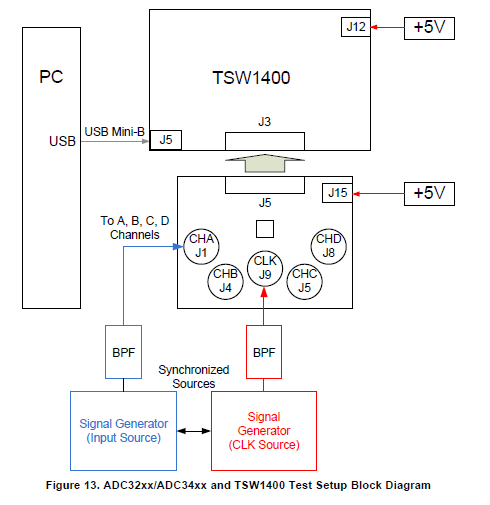

你好,你说的是否是像JESD204B那样,CLK和SYSREF分别接ADC和FPGA:

但是我看ADC324X,只给了ADC一个SYSREF和CLK,并不需要给FPGA一个SYSREF和CLK信号,现在有点迷糊了。望指教。