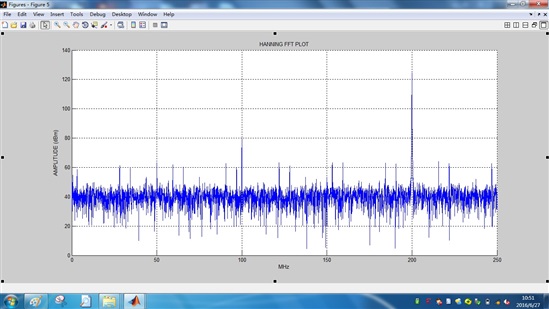

ADS5407输出采集信号频域底噪很差(见附件图片)

ADS5407两通道输出采集信号频域很差,当0E,0F和38寄存器中很sync相关位disable掉后(sync 15.625MHz仍就正常给)底噪就会变好。一改成sync input脚后又会变差。

ADS5407两通道输出采集信号频域很差,当0E,0F和38寄存器中很sync相关位disable掉后(sync 15.625MHz仍就正常给)底噪就会变好。一改成sync input脚后又会变差。

500MHz时钟和输入信号都有接滤波器。

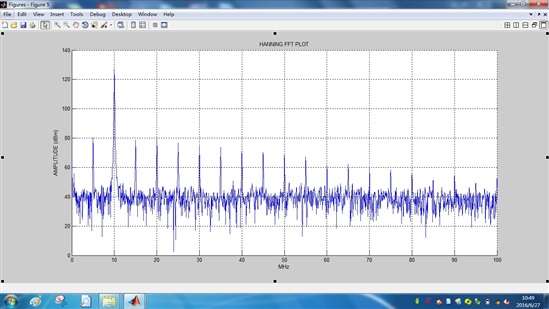

另外当输入信号为10MHz,频域5MHz和15MHz等地方也有(见图所示)。当输入信号为其它频点时就很好。

你好:

请问是evm还是你自己的板子?这个器件在国内是需要License的,推荐你使用ADS54t04或ads58c20.

如果是sync导致的可能和时钟时序相关。

另外一个问题看上去谐波比较高,匹配有些问题

如果不是需要多片5407同步同时输出的话,SYNC功能不要使能

同步信号可以改成一次触发的那种试一下

我现在192路AD同步就是需要sync功能来实现,不可能关掉。回答能说点实质性的东西么?现在我就想知道是什么原因导致采集数据整个频域上都出现干扰信号,是ADS5407采样时钟干扰或是其他的原因。

公司自己做的板子。采样时钟和sync信号都是AD9516-3出的,尝试用FPGA的PLL根据采样时钟输出一个15.625MHz给ADS5407作为SYNC信号,发现现象一样,仍就没有任何改善。采样时钟通过AD9516-3或者外接信号源给时钟buffer 1212一分多给8片ADS5407使用。另外你说的匹配有些问题是指什么匹配?时钟接入匹配还是sync信号接入匹配?能说详细点么?

ADS5407的sync是不是有bug?之前syncout一直都无法输出,后来根据论坛上另一个工程师帖子的建议将01寄存器的D2位设置成"1"(手册上该位标为“0”)后syncout才正常输出的。

你目前所遇到情况可能不止一个问题:

请问你是否有测试过TEST PATTERN以保证每个adc的数字接口都没有误码,如果数据位有错也有可能这种现象.

你 sync的周期和占空比是否正确,使用sync和关闭sync数据时钟时序是否有变化?开关sync导致数据有误很可能是时序临界导致的,请用示波器仔细看下时序。

你输入信号来源,是否良好差分匹配,差分是否平衡;输入模拟差分不平衡或匹配不好也可能谐波高。

高速信号设计要考量的东西比较多,你的路数太多,一个9516+14个1212应该也不够。如果多个,他们之间的同步也是一个问题,因此推荐你使用LMK0480x;

另外有关License问题,及你们系统的复杂程度,可以留下联系方式或直接联系销售人员;

我现在在FPGA内只建一个2通道的小测试工程,采出来的数据用matlab分析结果都这样。