为了防止缓冲器LMV321(电压跟随器)震荡,实际的电路中该预留哪些措施呢?

请问各位:

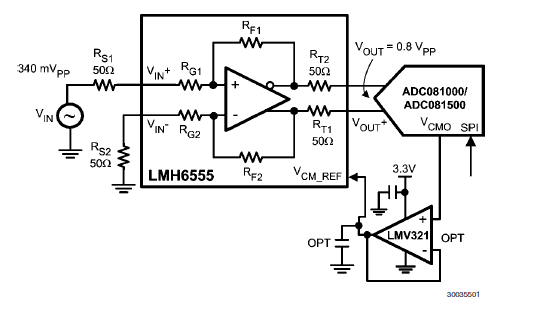

在使用差分放大器LMH6555作为ADC08D1020输入信号单端转差分的驱动器,ADC08D1020芯片资料上推荐使用时LMV321作为ADC08D1020的VCMO连到 LMH6555的VCM_REF端的缓冲器,详见下图。但电压跟随器这种放大电路在实际使用中很容易产生震荡,为了防止LMV321震荡,实际的电路中该预留哪些措施呢?敬请详解

手册很多都会提到G=1的时候稳定,即射随不振荡。 在上图电路中如果振荡有可能是输出端那个电容的影响,建议在输出电容与运放输出端加个0欧姆电阻备用。振荡了可以换个几欧姆小电阻。

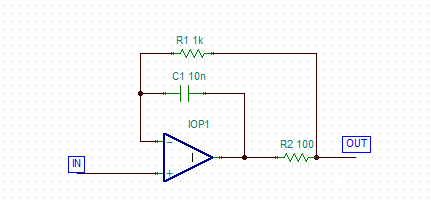

你好,可以使用这种电路:

请教Carter, 这个电路该如何理解呢?已知R2,C2(R2,C2构成 RC LP 滤波),如何计算R1,C1 呢?

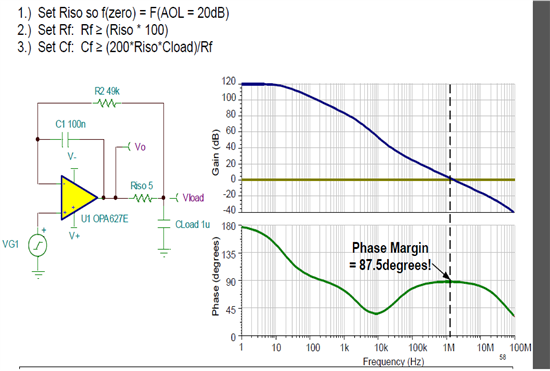

你好,当跟随器接容性负载时容易引起振铃及震荡,在输出端使用接电容后再接反馈,可以稳定输出。计算如下:

学习了,谢谢!

请教Carter,关于ADC08D1020芯片的Vcmo输出管脚电平的问题,是这样的,现在pcb板上ADC08D1020是用了一个AD驱动器驱动,AD驱动器是带共模输入电压的,所以需要ADC08D1020给AD驱动器一个共模电压,按照ADC08D1020的datasheet第43页描述的,经过一个lmv321,到AD驱动器,现在我让ADC08D1020上电,给PD管脚一个低电平,然后测试AD的Vcmo输出电平,是1.83V,但是按照手册上说的是最大才1.45V,现在不清楚为啥那么大的电压?期待您的回复

您好,输出1.83V是不正常的,不知道PDQ引脚是高电平还是低电平?

另外供电电压是多少?

最好能上传一下原理图啊

我把PD和PDQ都是拉低的,供电电压是1.9V,数字和模拟都是1.9V,原理图我是参照TI的评估板的原理图,附件中就是这个评估板的原理图。

期待你的回复哦

我是直接给AD上电,前级还没有给AD数据,把PD和PDQ拉低,直接测Vcmo输出的电压,就是1.83V,不晓得这样的测量方式正确不,然后Vcmo通过一个LMV321的放大器,将输出连接到一个AD驱动的Vcmo输入脚,相当于是想利用AD输出的共模电压将前级AD驱动的输出拉到AD所需要的共模电平,但是实际上测量AD的Vcmo的输出不是1.26V,而是1.83V

你好,你测试一下电源电压是否稳定,最好使用实验室稳压电源试试,另外看看这个引脚有没有跟其他地方短路;另外你做了几块啊,是不是每一块都这样?按道理说按照评估板上的原理图是没问题的

另外请按照我给你的这份参考进行设计:2870.ADC08(D)XXXX Schematic r2p4.pdf

恩,现在最新的情况是,我不考虑共模电平1.83V正不正常,直接供给AD驱动,然后看通过AD进行采样送到FPGA里面看数据,情况是AD的I通道能采数据,Q通道不能采数据,PD和PDQ都是拉低的。

f(zero)、F(AOL)代表什么意思呢?他们和Riso是什么换算关系呢?我还是不明白Riso怎么计算