ADS5560干扰问题

采用ADS5560作为ADC进行信号采集,输入时钟为25MHz,测量发现:

数字端不接负载,模拟端噪声共模5mv以内。

数字端(特别是CLKOUT)如果有负载(即使是10k电阻),对模拟端(VCM、INP、INM)都会有较大干扰(共模噪声Vpp可达到30mv-200mv)

请问这是什么原因?有何解决的好办法?

1. 你所谓的“对模拟端有较大干扰”是采完之后用数字量计算的,还是直接在模拟输入端用万用表量的?如果是在数字量计算的,那也有可能是接口的问题。

2. 数字端为什么要接10K的负载,有必要?DDR LVDS的输出,只需要在FPGA的数据接收引脚上端接50欧姆电阻就可以了。这个不需要上拉下拉之类,检查一下你的端接。

3. 最好能够上传电路图,以方便分析。

首先感谢您的帮助!

依据数据手册,采用模拟数字地相连,电源分别供电设计,采用芯片内部提供vcm,数字端为cmos输出模式接到上位机(FPGA)的。

发现:

1.芯片配置好后如果将数字端断接是没有什么问题的,但是将数字端与上位机相连后VCM端口用示波器测量时发现有较大噪声(100-200mVpp)。

2.采用SN74AVC16827DGVR芯片作为缓冲器(电源另供,与ADC模拟数字均非同一电源),VCM端效果无改善

1. 模拟地和数字地是分开的地平面,通过磁珠连接的?ADC的数字电和数字地,和FPGA的数字电和数字地,有什么瓜葛么?

2. 你的时钟模式,用的是default mode还是low speed mode?改一下有改善么?

3. VCM这个引脚有没有加0.1uF的滤波电容?

4. 最好上传一下电路图,方便分析。

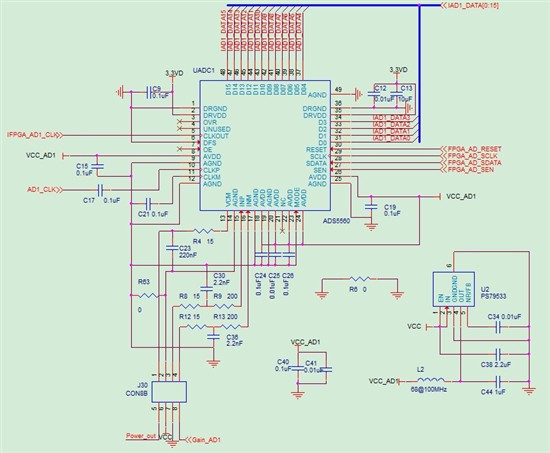

不好意思,前一段时间有其他事情处理,离开了一段时间…下面把电路图上传一下,请求帮助:

ADC&AVDD

外部数字地和模拟地是分开的,但是根据数据手册可以知道芯片内部其实已经相连…

DRVDD

目前发现:

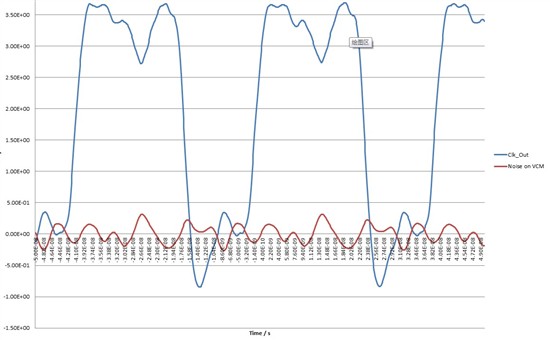

数字端接负载后,发现参考电压输出端带有了较大的噪声并猜测与输出信号具有一定的关系:(示波器)

所以目前怀疑是带负载后因为阻抗不匹配带来的地弹?这种考虑是否合理?但为何数字端的问题会影响到模拟端?而且将参考电压输出端到地的电容去掉后噪声依旧?

另外还有一种怀疑是发现ADC的模拟供电需求远高于数字供电的需求,而设计中VCM是ADC芯片内部提供的,那在ADC工作时会不会因为需要对参考电压进行多次较大量的电荷抽取而引起这种噪声呢?

内部提供的参考电压可带动多大负载?在接到前端探头的时候是否需要接一级跟随?

望不吝赐教,谢谢!

附:示波器测量信号及噪声的数据

1. “外部数字地和模拟地是分开的,但是根据数据手册可以知道芯片内部其实已经相连…”这个在手册多少页?

2. 如果采用内部基准,最好采用图49那种方式连接,抗干扰能力要好一些。另外,你电路图里VCM只是当做是一个测试用引脚输出,你能够保证VINP和VINN的共模电压等于VCM?

3. 可以考虑用作LVDS模式,如果FPGA测有内部端接电阻的话。LVDS模式的干扰要比CMOS模式小一些。

4. 你是从哪里买到这颗芯片的?

1.关于地相连问题重新看了下手册,在44页Board Design Considerations中有说明一个地就可以了,没有说内部相连问题。

2.ADC是有前端的,这里只是对ADC提供参考电压的接口进行的电压测量,发现了问题。

3.目前基本认定问题是ADC的高速I/O口较多,分布电感及阻抗不匹配带来的问题,想请教下有没有好的布板建议以及解决方案?

4.应该不是芯片问题(多家代理拿到的芯片)

把和VCM脚连接的15欧姆电阻R4换成个0欧姆试试。至于高速IO口,个人经验,用LVDS接口比用CMOS接口要好,高速下串扰和抗干扰能力都要好一些。

请问你是怎么驱动ADS5560的,有采集程序吗,速度那么高,你采的数是怎么存储的?初学者请求帮助