ADS1253驱动程序的问题

好吧,我又来问关于ADS1253的问题了,希望能得到TI工程师的帮助,谢谢!

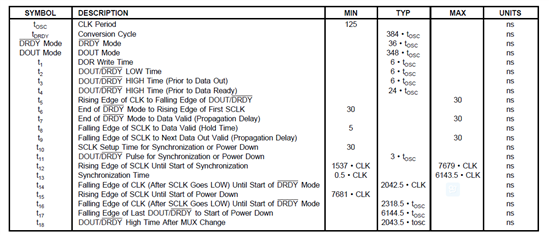

在ADS1253的规格书中,有三种工作模式:DOUT/DRDY ; SYNCHRONIZING MULTIPLE CONVERTERS ;POWER-DOWN MODE

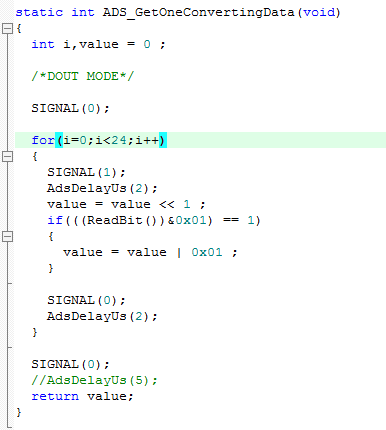

在我的程序中,只用到第一种工作模式:DOUT/DRDY,需要采集4路ADC数据,按照规格书中的时序图及项目需求,个人理解如下:

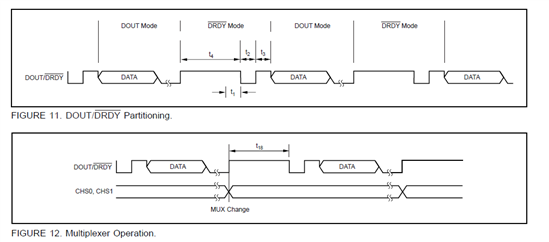

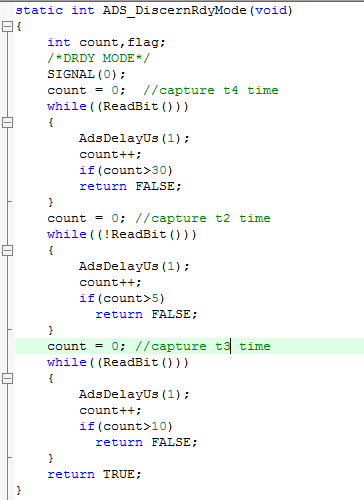

步骤①:先选择通道0,然后读引脚9:DOUT/DRDY 的数值,它肯定会经历一个t4(约为8us的高电平) , t2(2us的低电平) ,t3(2us的低电平) 的data ready(DRDY Mode)模式,在获取这个模式之后,读取24位寄存器DOR的数据,读取完第一次数据之后,重新捕捉data ready模式,继续读取第二个24位的数据,直到在该通道读取了50个数据。

步骤②:然后改变CHS0,CHS1切换通道,然后读取引脚9:DOUT/DRDY 的数值,参考附图下图FIGURE 12:Multiplexer Operation,引脚DOUT/DRDY会保存高电平输出t18(大约665us),

程序捕捉t18该状态,然后循环步骤①,从第二通道读取50个数据。

步骤③:循环执行上述步骤①和②,直到每个通道都读取50个数据。

使用的是外部CLK:3.072MHz,使用示波器能观察到晶振已正常工作;使用IO口模拟SCLK和DOUT/DRDY引脚。

现如今遇到的问题是:

在一个通道内,每次读取一个数值时,采样值是正确的。但在该通道内读取第二个数据时,无法捕捉到data ready(DRDY Mode)模式中的t4时刻。

读取data ready(DRDY Mode)模式的代码见下图:

读取24位数值的代码见下图:

楼主手册看得很仔细,不过我想是不是借助示波器认真捕捉一下时序波形验证一下?

嗯,有用示波器抓图。现在的问题是在通道切换之后,程序无法捕捉t18(约665us的高电平),但是如果程序不捕捉这个高电平而是延时665us,ADS1253却能正确读取4路转换结果。不知道是什么原因,难道在捕捉t18时,需要SCLK配合?规格书中并未说明捕捉该18时刻时,SCLK的时钟输出。