求助 ISO7230M 输出通道偶发输出低电平问题~~!

时间:10-02

整理:3721RD

点击:

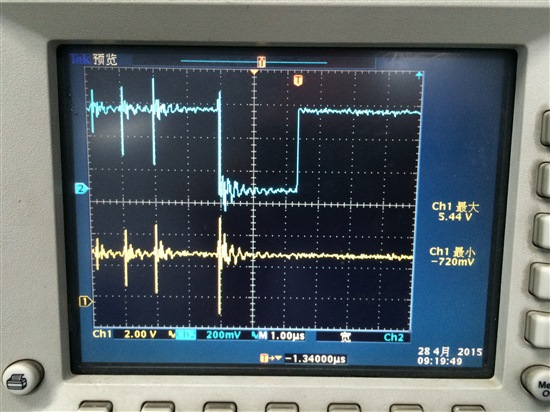

示波器通道1监测输入通道A(input)一直为高电平,高电平时偶尔有干扰,但是示波器通道2监测输出通道A(output)由高电平变为了低电平。而低电平的脉宽在2us~17us不等,请大神们解答为什么输入高电平时输出确偶发了低电平?查资料发现 failsafe operation 时output 是高电平,而资料上又写了咨询TI failsafe operation 输出低电平模式。iso764x系列资料上写了failsafe operation是输出为低,不知道ISO7230M 有无此模式?求大神指点! (ISO7230M三个通道都有相同现象,非通道损坏。)

这是个很严重的问题。从波形看应该是这个毛刺的干扰引起的,那你的着力先解决掉这个幅度过大的毛刺

ISO7230M内部也有failsafe保护电路,当输入为无效的逻辑电平时,输出应该是高电平,这个在真值表中也能体现出来。

无效电平时,输出高电平,但是从波形来看输入是高电平的时候,为什么输出出现了低电平? 我拿信号发生器做试验输入端大于100ns的信号时,输出端才有可能出现方波,而示波器抓取的波形来看,输入端高电平明显大于100ns了可是输出端却出现了低电平。

我拿信号发生器做试验,输入端大于100ns的信号时,输出端才有可能出现方波(方波的脉宽和输入端达到门限时波形脉宽一致),信号小于100ns时,输出端波形基本于输入端波形一致。示波器抓取的波形来看,前两次出现毛刺时,输出端信号同步。为什么第三个毛刺过后输入端还是高电平,输出端却出现了低电平,低电平的脉宽和毛刺低电平脉宽不一致?