ADC12D1800时钟芯片选择

目前我采用的芯片为ADC12D18000,工作方式主要有三种:

第一种采用两个芯片构成4通道,也就是2个ADC正常工作,采样率为500MSPS,工作时钟500MHZ,工作状态为NON-DES Mode ;

第二种采用2通道,一片ADC正常工作,另外一个ADC处于POWER DOWN状态,数据采样率为2GSPS,利用内部的DES模式,工作时钟为1GHZ;

第三种只用一个通道,一片ADC处于POWER Down,另一外一片ADC中的Q通道处于POWER DOWN,数据采样率为1GSPS,工作时钟为1GHZ;工作状态为NON-DES Mode ;

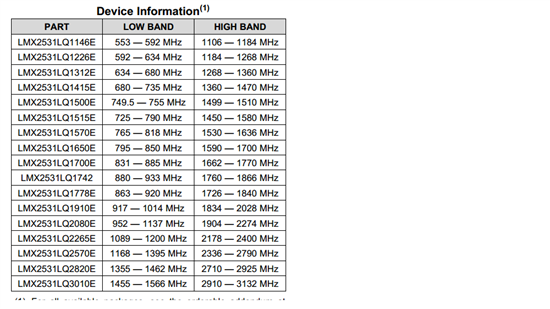

三种功能都是在同一板块上实现,通道模式的由FPGA控制,FPGA采用的型号为XC7VX485T。设计中推荐的时钟芯片为LMX2531显然不符合我的要求

问题:

1 时钟芯片的输入是LVCMOS,电平标准是3.3V,输入频率要包括10M和100M即可(最好额外还支持晶振输入,晶振频率无要求);类似IDT的8T49N287,资料见附件;

2 考虑系统时钟同步问题,所以我还需要产生200M或者250M,需要4路,所以相当于整个时钟芯片至少需要6路,其中2路需要能够达到500M和1G用于ADC工作时钟;

3 关于电平标准,由于ADC的工作电源为1.9V,FPGA的工作电压为1.8V,数据时钟和数据信号可以直接输送给FPGA处理吗,需要电平转换不。 FPGA资料见路径:http://xgoogle.xilinx.com/search?output=xml_no_dtd&ie=UTF-8&oe=UTF-8&client=support_c&proxystylesheet=support_c&site=Answers_Docs_c&filter=0&resultsView=category&tab=sd&num=1000&sortBy=displayOrder&show_dynamic_navigation=1&sort=date%3AD%3AR%3Ad1&documentClass=Document&requiredfields=-Archived%3Atrue&getfields=*&q=+inmeta:Document%2520Type%3DData%2520Sheets+inmeta:Devices%3DVirtex%252D7+inmeta:Document%2520Class%3DDocument+inmeta:Product%2520Type%3DSilicon%2520Devices&dnavs=inmeta:Document%2520Type%3DData%2520Sheets+inmeta:Devices%3DVirtex%252D7+inmeta:Document%2520Class%3DDocument+inmeta:Product%2520Type%3DSilicon%2520Devices

文件名:DS183

4 ADC的电源依据手册说要线性电源,可否采用开关电源,如果有好的建议,请推荐。

5 依据现有资料表明,ADC的所有地都应该统一为一种地,也就是说只分区不分地,请问有相关的理论文档不。

谢谢!

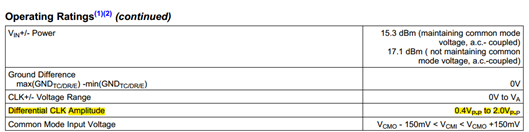

ADC12D1800 的手册提到, CLK 输入信号要求 0~Va (最大2.2V) , 但是没有看见推荐 LMX2531 这个器件做时钟.

时钟的输出信号幅度过大, 是不是可以考虑阻容电路之类的简单无源电路降下来.

首先,谢谢回复!

第一:之所以说到LMX2531的资料,主要是官网有一个关于GSPS 的ADC推荐手册,主要见附件,有一个时钟芯片,LMX2531的简易技术规格见下图说是

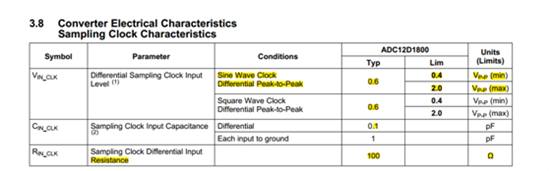

第二:关于ADC12D1800的时钟要求见下图,依据数据手册对电平标准没有要求,LVDS和LVPECL都可以,但是TI提供的高频率时钟电压都达到了3.3V。

至于你说的阻容电路降下来,有点不明白:1 如何降;2采用这种方式,时钟信号会不会有影响!

希望更多的人能够参与进来!

时钟用LMX2581吧。2531的焊接需要额外控制一下的。

也可以看看LMK0480x系列的芯片。

理论上仔细设计DCDC电源,也可以达到同样的效果,但是实际中很难的。用LDO吧,还要用high psrr的LDO

如果你的板卡比较简单的话,可以考虑分割地平面,但是要仔细考虑电流回流路径

此处我已经得到确认,跟大家分享一下:

LVDS_18 LVDS_25&LVDS_33都是LVDS的标准,之所以不同关键在于LVDS的缓冲器的电压不一样,在设计的时候,只要关注LVDS的共模电压和相匹配的输入、输出差分摆幅即可,需要关注接口的缓冲器的供电电特性。

谢谢了,最终我选择了ADI的AD9516-3,很适合本芯片和我的需求,谢谢

9516的性能不行。

你可以研究一下jitter对ADC SNR的影响。公式很简单的

可以具体说一下嘛!?

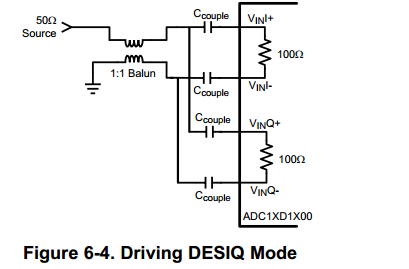

另外还有一个问题:我需要启动1路2G采样率,则需要使用DES_MODE模式,按照数据手册的第55页,描述关于Driving the ADC in DES MODE中可以有三种模式分别为:

1 单独接1路I通道,也即是DESI模式;

2 单独接Q通道,即是DESQ模式;

3 I通道和Q通道全部接入,也就是DESIQ模式;这种方式见图所示。

问题:要实现我的目的,一定要采用DESIQ模式?

http://www.ti.com/tool/jitter-snr-calc

SNR=-20*log10(Fin*Jitter_total)

9516的jitter可以在手册中找到,Fin是你的输入频率。

你好,TI工程师:

首先谢谢你的真诚回复!

关于你说的这个公式我看了,计算方式tj = ( Vinpp / Vinfsr ) x (1/(2^(n+1) xpi x fin ));我当做FIN=1GHZ处理;

为了计算简单将VINPP和VINFSR看做相等,n=12,在这样的计算方式下,得到了tj=0.04ps。查看ADC12D1800数据手册中Aperture Jitter为0.2ps

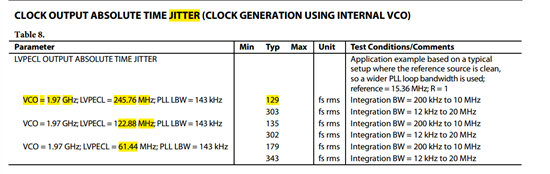

时钟的就利用AD9516-3的典型数据225fs,有可能更小,理论依据看图1所示,频率越高,抖动似乎越小,我的VCO应该会设置为2G,便于分频处理。

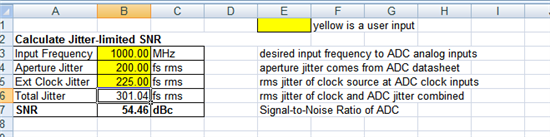

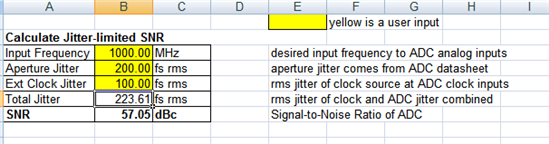

在根据你推荐的软件计算公式,外部时钟为设置了两个,一个为225fs,一个为100ps,得到的数值见图2和图3所示。

图1

图2

图3

好吧!问题来了,一般这种设计,SNR经验值必须得达到多少是最好的,希望不要告诉我是越高越好,谢谢!

查看到一个信噪比理想值计算方式SNR=6.02N+1.76dB,N为分辨率,得到理论值为74。ADC12D1800在实现2G采样率下需要达到什么条件。

谢谢!

继续:

在图2中如果得到了57,在根据理论计算公司ENOB=(SNR-1.76)/6.02,得到了9.17,蛮好的啊,如此计算!

SNR值是你系统要求的。先确定系统要求多少的SNR后,才能反推要多少的jitter的时钟。

225fs是9516的理论值,你做不到的

9516的LVDS最大输出是800MH

谢谢你的回复:

其实系统SNR我能说我不知道嘛,嘿嘿!

我只能说我的ENOB是需要9bit,那么反推得到了SNOR,也就是我上面那些图。关于你说的那个225fs典型值,似乎是对整个芯片的说明,看图1,我说了我的需求,反推频率按理应该可以得到更好的值,也就是100fs。

谢谢!

另外可以帮我解答一下那个DESIQ和DESI、DESQ三种模式!谢谢

我使用LVPECL电平标准,其余的LVDS是供给其他系统使用,查看了输入输出电平标准,可以符合我的设计参数,谢谢