ADS1178读的数据全部为0

时间:10-02

整理:3721RD

点击:

关于ADS1178:

当前我们使用SPI数据模式.CLK的频率为250K.通道为全部有效,高电平状态.发送SYNC信号后,接收到DRDY信号下降沿,读取不到数据,全部为低电平.电路图如下所示.

请问是什么原因造成的?

FORMAT[2:0]是在悬空状态?

FORMAT[2:0]是全部接地.

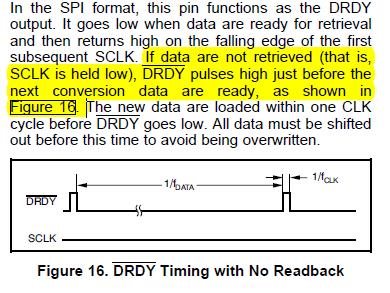

如果外部配置正确,在没有读取的状态下(SCLK一直是低电平),drdy信号是一个方波信号,每一个高电平表示数据转换完成一次,建议先检查有没有这个脉冲信号

sclk没有办法为一直为低电平,

drdy方波,

但是,文档中说是低电为数据完成标志

低电平时数据完成标志对的,如果不读取,正常情况下波形是这样的:

现在我们的情况是这样的,CLK与SCLK是同一个信号,用CPU模拟时钟把信号加载到ADS1178里.

如果ADS1178没有CLK信号,是否可以工作呢?

没有CLK信号肯定是不能工作的。

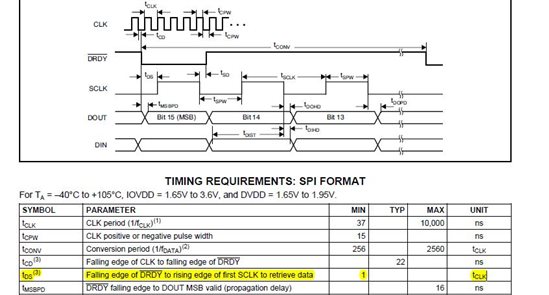

SCLK和CLK速率可以使相同的,但是不能是同一信号,请参考如下时序:

如果是同一时钟源,你怎么控制SCLK的时序呢,CLK不能停

我们现在的CLK与SCLK的信号是接在一起的.DRDY的信号是正常的.这点就让人比较郁闷了.所有的过程都是正常的.但是数据出来的为0或者全部为1.

请用示波器量下DRDY,CLK以及DOUT的时序,看下DRDY下降沿到DOUT的最高位数据的传输 延迟为多少,即tMSBPD时间。