求教ADS7830抗ESD干扰方法

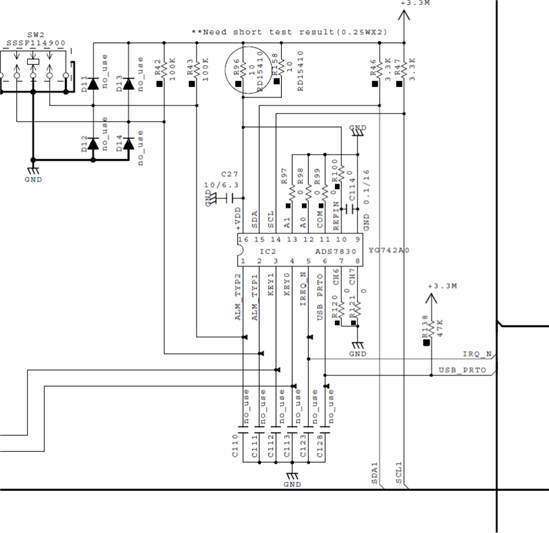

我在用ADS7830做一个按键检测,在做3KV ESD测试时,ESD信号打到外壳的地时,ADS7830会锁死。当ESD信号撤销后,改变ADC的输入信号,输出都是干扰前的数据。以下是我做的一些测试:

1. 在输入端对地我加了小电容(即C110,C111,C112,C113,C123,C128),没有效果。

2. 在VDD和地之间靠近ADS7830处加了一个0.1uF 的电容,也没有效果。

3. 在Vref对地和VDD对地间分别加了5V TVS管,也没有效果。

请问还有什么办法能改善抗ESD干扰?以下是原理图供参考。--谢谢。

亲;外联端口串电阻,改良PCB等都会有效果。具体做法需要看系统。

在输入端加ESD器件,试一试。仔细测试下,看看是从什么地方进去的。地,电源,信号端口?

电源若是使用的市电,可以在电源线加磁环、电源滤波器等优化电源;信号输入端可以加三端滤波器件试试。

另外,机壳内部所有板子使用单点接地,地线尽量粗。机壳接大地,导线要很与机壳接触良好,有漆的地方要打磨一下

多谢,

忘了说了,机壳是塑料的电源是通过adapter提供的,所以整个系统没有和大地的接点。并且内部是一块双面板,元器件布的比较密。这是比较麻烦的地方。

我现在从外壳的输入端子上想想办法。谢谢

多谢,我试过了,我将所有的输入,电源,参考都加了双向ESD管,没有效果。因为用双面板,而且元器件布的比较密,所以地面积可能不是太大。我现在想在打ESD的输入端试一下,看是否有效果?

不过有个很怪的现象,在输入端,原先有ESD保护管的,但是如果我拿掉的话,抗ESD的性能好像更好。你有何建议?谢谢

请参考ADS8688的PLC参考设计,这个设计可以通过如下实险。

(IEC-61000-4-4: EFT up to ±2KV @ 5KHz on signal ports; IEC-61000-4-2: ESD up to 4KV contact & 8KV air discharge; IEC-61000-4-5: Surge up to ±1KV line-earth (CM) on signal ports)

http://www.ti.com/tool/tida-00164