DDC264寄存器读出问题

我在使用4片DDC264记性级联, 进行寄存器配置的时候没有问题,随后也能读出来,但是不能确定只是哪片芯片的值。请问这个问题如何解决? 谢谢!

Hi Qing,

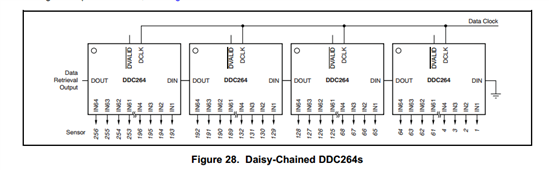

你说的 “记性级联” 是指像数据手册中Figure 28所示的菊花链连接吗?

你是说你读出的 寄存器配置 不确定是具体哪个芯片的配置吗? 4片DDC264的DIN_CFG, 和 CLK_CFG是怎么连接的?

菊花链连接下的转换值输出是依照数据手册中figure 29 所示依序输出的。

Br

Martin

Hi Martin,

不好意思,上面是输入错误,应该是“进行级联”, 就是指Figure 28所示的菊花链连接。 4片DDC264的DIN-CFG和CLK-CFG 都是连在一起的。 我说的数据不是指转换结果, 而是指芯片的配置寄存器的值,如Figure 33所示。 正常情况几个配置寄存器应该都是一样的,如果有异常配置寄存器值不一样的时候,我如何确定我读出来的值对应哪个芯片?谢谢!

Hi Qing,

还是跟数据手册Figure 33的时序一样,可以将所有的DDC264的配置信息从DOUT上读回来;

连接成菊花链的状况下,在写完配置寄存器后,在DCLK给320个时钟信号,然后第一个DDC264的配置就输出了,接着在给320个时钟信号,接着就输出了第二个DDC的配置,以此类推。 这个类似于数据手册图 29的时序,只不过输出的是配置信息,而且读出两个配置之间需要给320个时钟信号。

Br

Martin

你可以不连接在一起,一个一个进行读取,这个样就可以分清楚究竟是哪一片了。

不过这样弊端太大,如果能够容许的话,还是可以采用的。

连接成菊花链的状况下,在写完配置寄存器后,在DCLK给320个时钟信号,然后第一个DDC264的配置就输出了,接着在给320个时钟信号,接着就输出了第二个DDC的配置,以此类推。 这个类似于数据手册图 29的时序,只不过输出的是配置信息,而且读出两个配置之间需要给320个时钟信号。

建议你按照下图这个方法进行链接: