ADS1246输出不正常

输入0mv差分信号,输出值 3个字节为(00~FF跳动、00~FF跳动、00不变),输入4mv信号输出依旧不变,量过波形都正常也是下降沿采集数据,DRDY输出为1秒2000次,已经配置进去,基准2.048V,使用内部振荡器,求解问题所在,以下是配置程序

void InitADS1248(void)

{

cs_CS1242_1();//片选拉低

delay_us(10000);

nowp_ad1_eeprom();//START引脚至高

delay_us(10000);

reset_CS1242_1(); //复位

delay_us(10000);

noreset_CS1242_1();

delay_us(10000);

SPI_ADS1248_SendByte(ADS1248_CMD_RESET);//复位指令

delay_us(10000);

ADS1248WREG(0x00,0x01);//

delay_us(10000);

ADS1248WREG(0x01,0x00);//

delay_us(10000);

ADS1248WREG(0x02,0x00);//

delay_us(10000);

ADS1248WREG(0x03,0x7f);//

delay_us(10000);

}

void Ads1248(void)//读采集值

{

D=0;

//发送单次读数据命令

SPI_ADS1248_SendByte(ADS1248_CMD_RDATAC);

//读取ADC转换完成的数据

results1=SPI_ADS1248_SendByte(0xFF);

results2=SPI_ADS1248_SendByte(0xFF);

results3=SPI_ADS1248_SendByte(0xFF);

D|=results1<<16|results2<<8|results3;

//发送空操作指令,强迫D_OUT变高

SPI_ADS1248_SendByte(ADS1248_CMD_NOP);

}

void ADS1248WREG(unsigned char regaddr,unsigned char databyte)

{

//向寄存器写入数据地址

SPI_ADS1248_SendByte(ADS1248_CMD_WREG+(regaddr & 0xF));

//写入数据的个数n-1

SPI_ADS1248_SendByte(0);

//向regaddr地址指向的寄存器写入数据databyte

SPI_ADS1248_SendByte(databyte);

}

void ADS1248WREG(unsigned char regaddr,unsigned char databyte)

{

//向寄存器写入数据地址

SPI_ADS1248_SendByte(ADS1248_CMD_WREG+(regaddr & 0xF));

//写入数据的个数n-1

SPI_ADS1248_SendByte(0);

//向regaddr地址指向的寄存器写入数据databyte

SPI_ADS1248_SendByte(databyte);

}

Hi Zhenlei,

由于程序中包含了太多的子函数,不容易找出问题所在,

能否上传一下你的原理图, 以及通信过程中用示波器或逻辑分析仪测试的CS, SCLK, DIN, DOUT这几个引脚的时序图?

这样会更方便找出问题! 谢谢。。。

Br

Martin

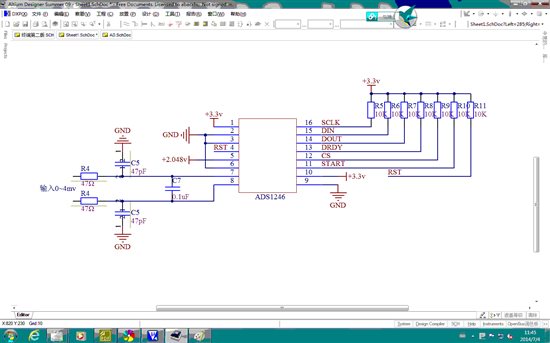

原理图

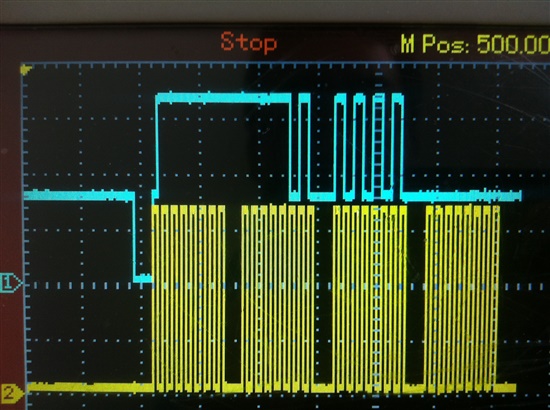

读转换数据 SCLK和DIN引脚波形

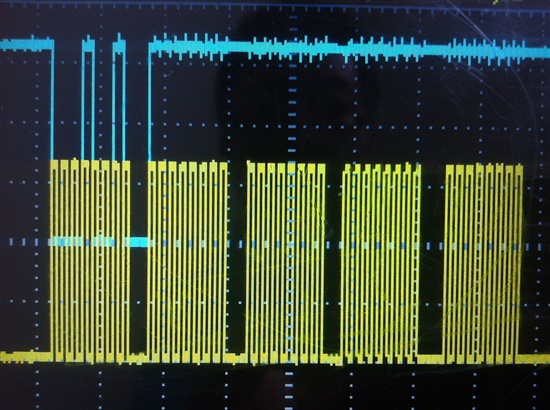

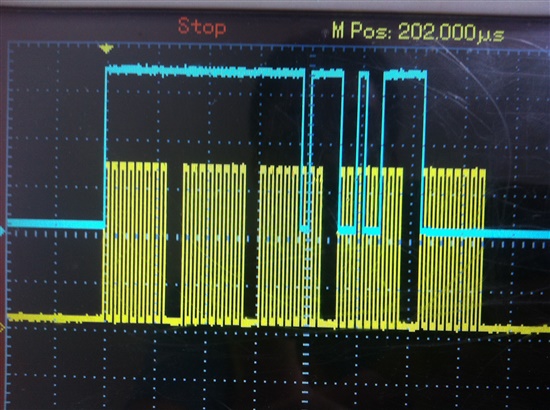

读转换数据SCLK和DOUT引脚波形

写错了 下面是SCLK和DIN波形 上面是SCLK河DOUT波形

您好,

从ADS1246的接口时序上看,在 START 引脚发送一个高电平脉冲后,需要等待到DRDY引脚变成低电平后再开始读取数据(如数据手册figure 67所示),程序中并没有等待到DRDY就直接读取数据了,这是造成读取数据混乱的主要原因。

ADS1246寄存器的配置需要依据数据手册figure 81所示,在地址前加入0100,在寄存器值之前加入0000,请检查是否正确;

时序截图最好能 将SRART, CLK, DOUT, DRDY 这几个引脚在4通道的示波器上同时截取出来,截取从START 的上升沿开始到所读取的最后一位输出;另外最好能上传一个放大后仅仅包含8个时钟周期的图,这样的话就能很明确地了解到时序是否有问题。

硬件连接中,PIN6 REFN 需要连接至AGND, DGND 跟AGND 需要分开布线,参考电压输入,模拟电压输入均需要良好的去耦,并非所有的数据线都要上拉电阻的,具体请参考EVM的连接:http://www.ti.com/general/docs/lit/getliterature.tsp?baseLiteratureNumber=sbau149&fileType=pdf

Br

Martin

刚才是不小心把DRDY和dout引脚短路了,正确的波形是下面

配置寄存器地址前加了x040和0x00,并且已经确定能够配置成数据更新率2000次

START引脚从上电开始就一直是高电平

上图是DRDY波形,下图是DOUT波形

Hi Zhenlei,

通信接口时序看起来没什么问题!

请依照我的上一个回帖修改硬件连接,特别是参考电压输入部分!能否将参考电压源的连接图发上来看一下?

另外,请问片内PGA你是怎么设置的?

Br

Martin

是不是与PCB布线有关呢?有没有把模拟地和数字地分开布线?可能会收到干扰。

ADS1246在 START 引脚发送一个高电平脉冲后,需要等待到DRDY引脚变成低电平后再开始读取数据,程序中并没有等待到DRDY就直接读取数据了,这是造成读取数据混乱的主要原因。时序截图最好能 将SRART, CLK, DOUT, DRDY 这几个引脚在4通道的示波器上同时截取出来,截取从START 的上升沿开始到所读取的最后一位输出;另外最好能上传一个放大后仅仅包含8个时钟周期的图,这样的话就能很明确地了解到时序是否有问题。

楼主布线有没有问题哦。可能与PCB布线有关,有没有把模拟地和数字地分开布线?这个EMI干扰很厉害的。。

zhenlei hu1

刚才是不小心把DRDY和dout引脚短路了,正确的波形是下面

配置寄存器地址前加了x040和0x00,并且已经确定能够配置成数据更新率2000次

START引脚从上电开始就一直是高电平

这个波形看起来应该是没有问题的,话说你是不是把蓝色的那个通道向上平移了?如果是向上平移了,那应该是正常的。