DAC5686 时钟问题请教

我用DAC5686 外部时钟模式,电路连接采用手册推荐电路 Figure48 Driving the DAC5686 With a Single-Ended TTL/CMOS Clock Source 右边的图,时钟信号由FPGA引脚输出,电平标准3.3VLVCOMS,对时钟的配置按照手册26页外部时钟部分推荐,当从FPGA提供的时钟小于120MHz,DAC工作正常。当提供的时钟超过120MHz,DAC无法正常工作,PLLLOCK引脚无输出,改变SEL[1:0]值仍无效,不知道什么原因,求指导

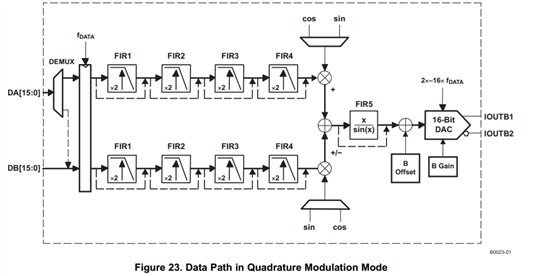

还有一个问题,DAC5686 提供了Full_bypass 功能,可以屏蔽掉所有内插滤波器,当我使用该功能时,即将config_lsb 寄存器的Full_bypass 位置1,DAC无法正常工作,所以必须使用内插滤波器,不知道该功能是怎么回事。

你能用仪器测一下时钟信号的质量嘛。

从你的描述像是内部时钟电路没有工作起来。

终于有人回复了,先感谢一下。我时钟电路用的是时钟芯片AD9912,经FPGA送往5686,当时钟频率升高时,质量会有变化,但不至于变得很差,送往5686的时钟用示波器看感觉还可以。我开始从FPGA输出的时钟用的是3.3VLVTTL电平,当时钟超过100MHz,5686就无法正常工作,后改成3.3vLVCOMS电平,时钟可以正常工作到110多MHz,当为120MHz时,5686输出信号质量明显下降。超过120MHz,5686无法工作。5686最高工作时钟是500MHz,我只要到200MHz就行,难道5686对输入时钟质量要求很高?本人经验不是很足,还希望各位大侠多指点一下

还有就是Full_bypass功能,这个应该与时钟无关,我5686正常工作时,该功能还是不能用,一使能,就无法正常工作,不使能就正常,难道必须要用内部的内插滤波器?

1. 数据率(datarate),随路时钟(clk1--data clock)以及DAC时钟(clk2-DAC clock)各是多少?是否用到内插?如果用到,几倍内插?首先确认一下这几个速率没问题。

2. 用外部时钟模式,内部的PLL是不是被bypass了?

3. 如果用内插,先确定data rate和DAC clock对得上,比如data rate是50M,4倍内插,那么DAC clock要严格给200M。

用的外部时钟,两倍内插,正常的话在芯片PLLLOCk引脚会生成一个输入时钟二分频的时钟信号,并用该时钟作为DAC的数据输入时钟,当我提供的clk2 输入时钟小于120MHz时,是正常的,比如,我提供一个100MHz时钟,PLLLOCK会生成一个50MHz的时钟,DAC正常工作,内部NCO也正常,当超过120MHz,PLLLCOK就没有输出了,NCO也不正常工作。

用外部时钟的时侯,电路是不给内部PLL模块供电的, 内部PLL应该是bypass了 ,所以clk1 的时钟我没有提供

按说PLLLOCK这个引脚的输出不应该和NCO扯上关系啊。参照图27检查下面几个问题

1. 如果是用的外部时钟模式,先用万用表量一下PLLVDD,确认这个引脚电压是0而非不定态。

2. 检查SEL[1:0]的值写的是多少。2x内插时应该是0x00。

3. 用PHSTR同步一下(给一个低到高的脉冲)是否有改善?

我主要用5686做IQ调制用的,所以要用内部NCO,我现在测试时钟工作范围就是通过测是NCO输出,我I路提供一个直流信号,Q路设为0 5686工作在Quadrature模式下,DAC B 路 正常输出就是载波频率,当外部输入时钟在120MHz以内,一切都正常,当超过120MHz就没输出了,测试PLLLOCK也无输出

您给提的这三个问题都检测过了,PLLVDD 是0V SEL[1:0] 设置的是0x00 2X内插,关于这个设置我其他内插倍数也试过,输入时钟低于120MHz都正常,超过120MHz无论设置什么都无输出。

PHSTR同步也试过了,还是没用

真心不知道还有什么可能导致不能正常工作 还请大侠们指教啊

看了一下AD9912的手册,CMOS输出速率最高到150M @3.3V,如果仅仅是从9912里出来经过FPGA简单buffer一下,可能还跑不到120M,时钟质量就会很差了。

再者,不知道FPGA的时钟输出口可以支持到多大速率,你的FPGA型号是什么?可以把关于FPGA时钟输出口的相关信息发上来么?

从DAC5686的手册第10页来看,CMOS接口的输入电容是5pF,在这样一个容性负载下,如果从FPGA过来的时钟驱动能力不够,造成的结果就是明显的上升时间和下降时间。这样一来,DAC内部的时钟分频,分下来的时钟,占空比就会越来越小,以至于最后可能输出的PLLLOCK没有1,全是0。所以现在可以去查查FPGA芯片对于时钟输出口的驱动能力之类的信息。

另外,5系列的DAC是很老的型号了,为啥不用新的DAC3482?DAC3482+TRF3705是完整的正交调制解决方案,支持单发,性能比5系列的好太多。

真心感谢您一直指导

9912手册上说 输出频率超过150MHz,用HSTL输出。所以我9912 用的输出是HSTL差分输出,经过一个MAX9378 转成LVDS电平然后送到FPGA, FPGA用的是Straticx II EP2S30F672 。时钟信号从Bank 3 的一个通用IO口 输出给5686了,开始时Bank3 电平标准是3.3vLVTTL,送给5686的时钟超过100MHz就不能正常工作了,后改成3.3VLVCMOS ,工作时钟就到120MHz了。因为在原理图设计的时候就是将bank3 的这个通用IO口直接连到了5686外部时钟输入引脚上了。用示波器测的从FPGA输出的时钟随着频率上升质量会下降,难道真是时钟质量达不到5686的要求,才不能工作的,这可怎么办啊。

当时做这个正交调制的时候,是看了TI的一个讲DAC的资料,其中介绍了有关正交调制的内容,然后我在器件选型的时候就在TI网站上找有NCO模块的DAC芯片,考虑到功耗问题就选了5686,当时就想通过一片DAC实现正交调制,对于数字调制如QPSK QAM 8PSK等,直接将I Q两路数字信号送往DAC与其 内部NCO生成的正交载波相乘在加即可,通过电路实测也确实可以,但对于模拟调制如FM AM这样确不太行,是不是就是要讲I Q两路信号转换成模拟信号在用您给推荐的正交调制器实现呢?还有就是在做正交调制的时候,无论哪种调制方式, 都应该将I Q两路信号转成模拟信号输出 在与两路正交载波乘加实现呢

从以往的经验来看,DATACLK可以从FPGA出,但是从来没有哪个项目里,DACCLK可以从FPGA里出。原因有二:一是FPGA的时钟没办法做到低抖动,DAC需要的时钟需要抖动要控制在几百个fs,越低越好。但是FPGA里出来的时钟,抖动恐怕要上ps级了,这种时钟给DAC供,风险很大。二是FPGA的时钟摆率有限,很难说在高频时还能够维持够短的上升和下降时间。像这种高速应用里,最好使用安捷伦的E5052信号分析仪去测时钟的相噪,或者退一步,用便宜的R&S频谱仪装个插件,测相噪。用示波器看时钟的“相噪”或者时域抖动,没有任何意义,因为示波器本身达不到那么高的采样率,也很难做到很低的加性抖动。

之前有人贪便宜,用FPGA出DACCLK,结果直接DAC输出不正常,最后解决的办法是换了一个LMK0300x时钟产生芯片,才让DAC工作正常。所以建议是换时钟,换LMK04906或者LMK0480x,最差也要换个LMK03000。如果硬件做死,换不了,就只能跑较低的时钟速率了,但是高低温下仍然有风险。

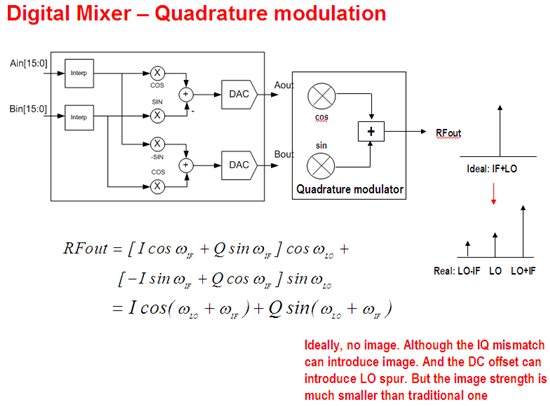

关于正交调制部分,初衷是干掉镜像,你可以参考一下下面这张图片,应该会对你有帮助。

之前用AD9747就是从FPGA引脚直接引出的时钟,不过是直接从FPGA专用的锁相环时钟输出引脚引出的差分信号,9747在200MHz时钟下可正常工作,然后用5686,我电路是双时钟都设计了,也是从FPGA锁相环时钟输出引脚引出了一对差分信号送往5686的Clk1 和clk1C ,那我现在用5686的锁相环时钟模式可行不。

在我们用DAC时,是不是最好通过外部时钟电路直接提供给DAC采样时钟信号,然后用DAC提供的数据时钟信号送回FPGA作为系统数据信号时钟来达到同步?

我电路想实现的是基带信号的输出及 AM FM QPSK BPSK QAM 等调制方式,载波频率要求也不高,就是10MHz到40MHz,我仅仅是将基带信号上到中频,不需要在上变频到高频部分。所以就用了5686,用了一个简单的数字调制器实现正交调制。就相当于您给的图中到Aout那部分的输出。但我看现在的仪器或是您给推荐的两片芯片做正交调制 好像都是将IQ两路基带信号先转换成模拟信号输出,在用模拟调制器实现正交调制,请问如果我载波频率要求不高的情况下,是不是直接用一个数字调制器,如带NCO的DAC,将I Q两路数字信号直接送往该DAc就实现了正交调制呢(在不考虑镜像问题的情况下)?

TI比较新的DAC348x系列高速DAC,是有两套时钟,DATACLK和DACCLK。DATACLK用作FPGA发送数据的随路时钟,可以由FPGA发给DAC,用来锁存FPGA发过来的数据。DACCLK用作DAC工作时钟。DATACLK和DACCLK是两个时钟域,中间用FIFO缓冲。

IQ两路数据直接送到NCO,没法实现正交调制吧,DAC两路输出没有办法在DAC内部直接做和啊。

5686内部有正交调制模块,在IOUTB口输出正交调制结果。若果我基带信号上变频到中频,而5686内部NCO提供的载波频率足够,我是否直接用一片5686就可以 实现正交调制,而不用外部模拟调制器了呢

如果FPGA里已经把IQ两路数据按照先前我发的图片里的公式做过*cos,*sin的处理,形成DA,DB。然后DA,DB在DAC5686里用NCO做正交调制,理论上是可以得到单边带的中频信号的。这样在DAC后面直接接混频器(而非射频调制器),做上变频就行了。

如果FPGA里发的DA,DB就是原始的IQ,那么从DAC里出来的就是I*sinIF+Q*cosIF,如果此时后级用混频器,则混频器输出为I*sinIF*cosRF+Q*cosIF*cosRF,这种情况下本振两端会有幅度相同的信号和镜像。

在做数字调制如QAM QPSK 8PSK 等,例如QPSK 调制信号输出是Acos(wt+a),展开就是 Acos(wt)cosa-Asin(wt)sina,我将Acosa Asina 在FPGA内部映射成Q I,这样相当于直接从FPGA输出 I Q 两路数字信号,送往5686 ,从5686出来的不就是Qcos(wt)+Isin(wt),对应您说的就是 从DAC出来就是I*sinIF+Q*cosIF,这样不就达到了我要生成QPSK信号的目的了吗?我后级也不用接混频器了

您说的那种我看来更像是对于模拟调制,I Q两路都是模拟信号输出后,在对其进行上变频处理,数字调制是不是可以省掉将IQ 转成模拟输出这一步呢,还是说无论数字调制 还是模拟调制 均是要将IQ两路转成模拟信号,在上变频来实现调制信号输出呢?

混频器是单路信号直接乘以LO,调制器是A*cosRF+B*sinRF,都是上变频到射频,然后滤波放大后经天线发射的。看上去你的应用里不需要天线,只是需要得到一个中频(100~200MHz)即可?那确实就没必要用混频器或者调制器了。

FPGA里和DAC里都有NCO或正交调制的框图,你可以推一下公式,如果这样的框图里推出的公式符合你的要求,那其实就没有问题了。我也不太清楚你所谓的“数字调制”和“模拟调制”是什么意思。。。你想要的,不是一个DAC输出的模拟量么?不管用什么调制方法,最后总归要用一个DAC把数字量转化成模拟量啊。

我要的就是一个DAC输出的模拟量,谢谢您的一直指导,受教了,看来我还是有很多东西要去学啊

从以往的经验来看,DATACLK可以从FPGA出,但是从来没有哪个项目里,DACCLK可以从FPGA里出。原因有二:一是FPGA的时钟没办法做到低抖动,DAC需要的时钟需要抖动要控制在几百个fs,越低越好。但是FPGA里出来的时钟,抖动恐怕要上ps级了,这种时钟给DAC供,风险很大。二是FPGA的时钟摆率有限,很难说在高频时还能够维持够短的上升和下降时间。像这种高速应用里,最好使用安捷伦的E5052信号分析仪去测时钟的相噪,或者退一步,用便宜的R&S频谱仪装个插件,测相噪。用示波器看时钟的“相噪”或者时域抖动,没有任何意义,因为示波器本身达不到那么高的采样率,也很难做到很低的加性抖动。

之前有人贪便宜,用FPGA出DACCLK,结果直接DAC输出不正常,最后解决的办法是换了一个LMK0300x时钟产生芯片,才让DAC工作正常。所以建议是换时钟,换LMK04906或者LMK0480x,最差也要换个LMK03000。如果硬件做死,换不了,就只能跑较低的时钟速率了,但是高低温下仍然有风险。

正好对利用FPGA作DAC的同步转换时钟(DACCLK)有疑惑!这个回复给了我答案,看来上颗LMK03000是很有必要的,打算买一个LMK03000评估板。

请问这位大侠,我用FPGA同时控制ADC和DAC,在以下两种方法中该取哪一种?方法一:将LMK03000输出的3路时钟分别送给ADC、DAC和FPGA,作为ADCCLK、DACCLK和FPGA的工作时钟;方法二:通过FPGA产生DACCLK,然后送到LMK03000作消抖处理。

方法一固然好,但是对于SPI口的DAC,DACCLK与DATACLK的帧同步会有问题吗?如何控制?方法二同步控制看似更加容易,但是否可行呢,时钟抖动的抑制效果是不是不如方法一? 如果采用方法一,请大侠给一个对ADC和DAC同步控制的方法?先谢过了

DAC5686 DAC56867 DAC56868 DAC56869 这些芯片出厂先后顺序是什么啊?

DAC5x系列和DAC3x系列比,是老片子。那TI对老片子和新片子命名是什么规则啊?