求助:DAC5672芯片数据转换的问题

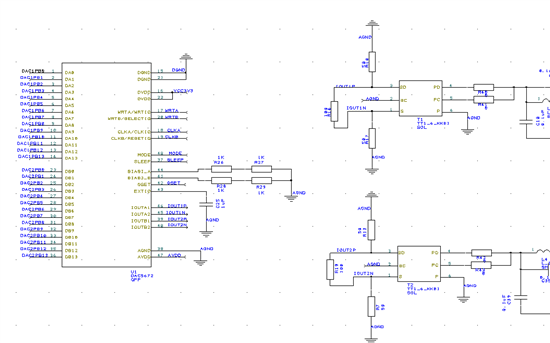

使用DAC5672做数据转换,FPGA与DAC5672相连,输出数据和写、时钟信号。

目前写和读写时钟信号都是6.25MHz,并且同相位。

14位数据都为高电平,按理说输出的模拟信号应该是一个1.2V的高电平,但是现在输出端没有任何信号。

mode为Dual-BusData,sleep也设置的对的。

请专家帮忙看看怎么回事,是不是与PCB走线有问题。

下面是相关的电路原理图,图上高地位弄反了,但是如果全为1的话,应该没有影响的吧。

你说的" 读写时钟信号"是什么意思?这个芯片应该不存在读吧.

这是一个275M的高速DAC, 输出电容5PF, 所以你想输出一个直流信号我觉得不合适.请输入交变信号测中射频性能

另外这是一个对于一个275 MSPS的高速DAC来说,6.25M的转换速率太低了,请提高

我写错了,是写信号,没有读信号。

我之前用的是50M的时钟,想输出一个三角波,也是没有波形。

这是我们的EVM板给你参考,你确认下相关的控制管脚和外围电路, 如果电路正确,加上时钟和数据后至少能有一些输出频谱

http://www.ti.com/tool/dac5672evm

还是dac5672的输出问题,我用100M的时钟和写信号,就可以输出波形,但是换成50M就不能输出。Robin Feng

这是我们的EVM板给你参考,你确认下相关的控制管脚和外围电路, 如果电路正确,加上时钟和数据后至少能有一些输出频谱

http://www.ti.com/tool/dac5672evm

这是什么问题呢?

如前面给你说的,高速DAC频率还是不能太低. 100M降50M你改了什么?100M可以证明硬件上应该没什么问题.

你看下是频率低,交流耦合幅度降低导致的. 还是软件上的问题.谢谢.

我只是把100M通过分频到50M的,其他的什么都没有改动。

EXIO输出脚上的电容大小会有问题吗?如果采用的是内部参考。

交流耦合幅度降低是什么意思呢?Robin Feng

如前面给你说的,高速DAC频率还是不能太低. 100M降50M你改了什么?100M可以证明硬件上应该没什么问题.

你看下是频率低,交流耦合幅度降低导致的. 还是软件上的问题.谢谢.

电容通交隔直,低频可能有衰减,你看信号到器件上是否都收到,幅度够

EXTIO参考的0.1uF旁路电容,没有影响

你好,输出的不是电流吗?

还有有什么办法测试数据的准确度?

怎么测数据的准确度?

如果有波形出来的话,可以根据datasheet中的转换公式计算输出的电压值,看一下和波形的值是否一致

DAC5672和DAC5672A虽然可以pin to pin,但是貌似软件上有差别。我DAC5672A调试出来了,DAC5672倒是没有波形,很奇怪!

你好,你有DAC5672的spice model 吗?如果有,可以给我吗?如果没有,那您是如何仿真的呢?非常感谢!

你好, 目前是有IBS模型, 下载地址如下,请你下载使用,谢谢

http://www.ti.com/product/DAC5672/toolssoftware

Models (1)

| Title | Category | Type | Size (KB) | Date | Views |

|---|---|---|---|---|---|

| DAC5672 IBIS Model (Rev. A) | IBIS Model | (Multiple Files) | 11 Aug 2008 | 1,101 views |

你好,IBIS model 能测试的比较少。有没有其他形式的model.例如spice model或 matlab model?