adc08200的时钟~~

时间:10-02

整理:3721RD

点击:

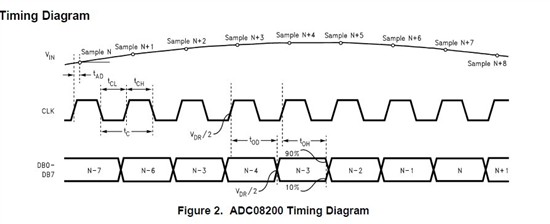

采用流水线结构,时序图:

\

\

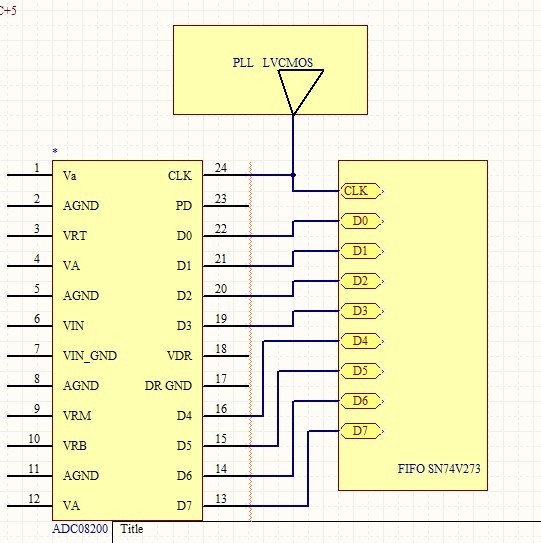

关于这个有两个疑问~这款AD和FIFO SN74V273对接

1 FIFO是在CLK的上升沿读数据并存储,而看AD的时序图似乎是在下降沿读取数据比较可靠稳定,需要给FIFO的时钟加个NOT门反相么?

因为AD的流水线结构会有6个时钟延迟,那么上电后第一个时钟,或者前六个时钟过来的时候,AD输出的是什么状态?高阻态?全0?

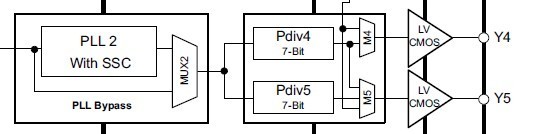

CDCE925这个PLL的输出

Y4,Y5是同相位的么??

1. 你为什么要加个FIFO而不直接进FPGA, 实际你ADC跑多快? 其实下降沿也在数据中间,一般FPGA里面也可以做FIFO且时序可调. 数据来之前总线上应该是不确定状态.

2.CDCE925的Y4和Y5是不同分频器出来的,不能保证完全同相位.

因为对FPGA并不是很熟悉...要开发FPGA周期就加长了好多

可以加个试一下,但是要注意它的delay。

最初的输出是乱数,对你没有意义的。系统一启动,你的程序还没有下载结束时,ADC的前几个数据就已经发出了,对你没有影响的

请问一下你们的ADC08200CIMT有ibis模型吗?