DAC3164

你好,在看DAC3164 的datasheet 时,遇到个问题。SYNC P/N 用来reset DAC内部的FIFO。我想问的是,该DAC内部的FIFO有多大,需要多少个dataclk后需reset?

谢谢~

FIFO可以存储8个samples.数据手册table1-4给出不同操作模式下的reset顺序。

谢谢你的答复~

我大概理解了,就是说在SDR模式下,可以送8组data[11:0]存入FIFO,如果此时继续存入数据会怎么样,即FIFO不复位? 会覆盖之前写的数据?

还有我大概存入小于8组的数据就复位可以吗?比如存一组数据就复位一次,即FIFO的复位信号SYNC 和 Dataclk 相同是否可以呢?

首先回答后面的问题,SYNC与Dataclk 是否可以相同:

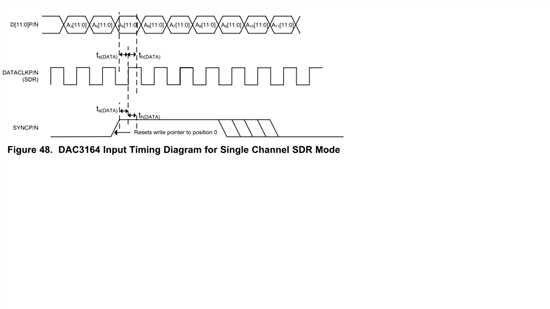

不可以,因为描述SYNCP/N是这样说的,Reset the FIFO or to be used as a syncing source. These two functions are captured with the rising edge

of DATACLKP/N. The signal captured by the falling edge of DATACLKP/N,也就是说SYPNCP/N是需要由DATACLKP/N的上升沿和下降沿来检测的,所以两者不能相同。

对于继续存入FIFO不复位或者小于8组数据就复位,我没有尝试过,建议不要这样做,可能会引起FIFO崩溃,不能正常工作,建议按照手册Table1-4进行操作。

datasheet上面的意思是送一组数据给DAC,sync复位一次?也就是SYNC时钟频率和DATACLK的频率是相同的,但是相位不同(最好相差半个周期,这样在DATACLK时钟上升沿或下降沿可以采到SYNC信息)

从这个图里可以看出,SYNC与DATACLK频率不同,SYNC只是复位写fifo,由于有8个fifo,所以没有必要写一次就更新,可以写8个(应该也可以小于8个)来一个SYNC信号,复位一下fifo。DATACLK是每组数据都要有的。这就是说SYNC的频率应该为DATACLK的1/8(如果写满fifo后置位)。如果小于8个,我觉得也可以。更正一下我之前的说法。

关于 SYNC/ALIGN 操作,可以参考一下

http://www.ti.com/litv/pdf/slaa584

尽管此文章是讲DAC348X系列, 但是同样的同步操作规则 可以应用在DAC317x, DAC316x 系列。

好的,了解了。

非常感谢~