adc08d1020的控制线(1.9V电平)接入 xilinx V5 电平为3.3V的IO BANK

adc08d1020的所有控制线(1.9V电平)接入 xilinx V5芯片 电平为3.3V的IO BANK,现板子已做好,没有办法换FPGA的IO电平。

控制线有三种:

1)可以直接接高电平(1.9v)或接地,这种可以通过上下拉电阻控制 。

2)FPGA输出脉冲给AD,即3.3V驱动1.9V 如Pin 30 CAL: Calibration Cycle Initiate.

3)AD输出脉冲给FPGA,即1.9V 驱动3.3V ,如Pin 126 CalRun:Calibration Running indication.

请问:

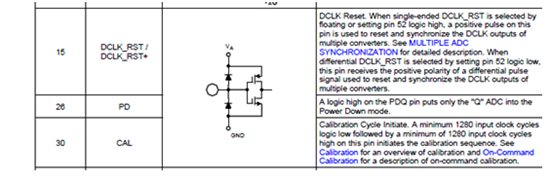

- 对于2)由于AD的输入端有钳位,VA =1.9V,如下图,是否3.3V驱动1.9V 没有问题?如果有问题该如何解决?

2. 对于3)AD输出高电平是不是驱动不了FPGA的逻辑1?(FPGA 用的是XILINX V5 )可有解决的办法?

您好,对于您的问题:

1.对于2)由于AD的输入端有钳位,VA =1.9V,如下图,是否3.3V驱动1.9V 没有问题?如果有问题该如何解决?

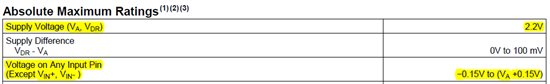

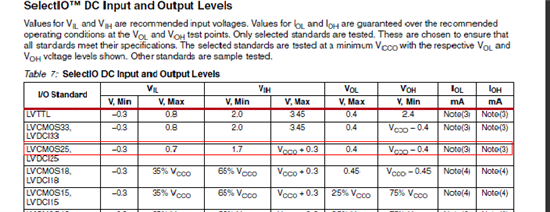

根据ADC的数据手册:

可见,FPGA的3.3V不能用。也说明ADC输入的箝位二极管导通电压不高。即使可以用,3.3V的摆幅远高于1.9V,也会限制ADC的数据通信速率。

2. 对于3)AD输出高电平是不是驱动不了FPGA的逻辑1?(FPGA 用的是XILINX V5 )可有解决的办法?

是否可以驱动,应该看看FPGA的手册中对高低电平阈值的要求,但1.9V作为高电平对3,3V而言确实低了点。

对1和2两个问题,都有类似的解决方法:使用信号电平转换芯片(voltage level translator),比如SN74AVC2T245,注意工作频率要满足ADC通信速率的要求。

谢谢您的回复,主要是加一个驱动芯片相对比较困难,除非再做一个板子。我想请问下面的问题:

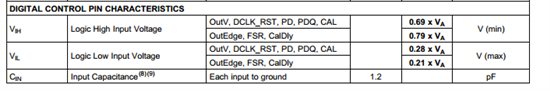

1. 对于2)芯片手册上有

其中OutV, DCLK_RST, PD, PDQ, CAL,OutEdge, FSR, CalDly都是输入AD的控制信号,它的高电平的最大输入电压并没有限制,这样可以认为从fpga输入3.3V的电压给AD满足要求可以吗?

2. 对于2) 3.3V的摆幅远高于1.9V,也会限制ADC的数据通信速率问题

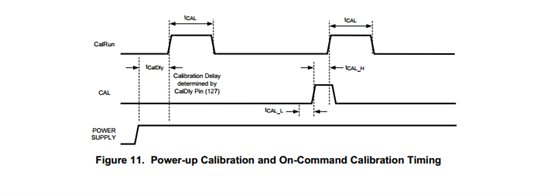

如果fpga给AD的脉冲控制信号(CAL)只是频率很低的脉冲,对于CAL较正初始化时序如下:

CAL:Calibration Cycle Initiate. A minimum 1280 input clock cycles logic low followed by a minimum of 1280 input clock cycles high on this pin initiates the calibration sequence

它基本上就是个单个脉冲,这样低的通讯速率会有影响吗?

3. 对于3)如果把AD的输出控制线 CalRun飞线至fpga VCCO=2.5v BANK 的差分管脚的P 管脚,同时对应的N管脚接地,同时约束为LVDS25;相当于AD输出的1.9V电平接入LVDS 2.5V的正端,副端接地;这样的差分输入是否可以驱动fpga逻辑高?

1. 不行,前面回给你的图里面已经说明了。

2.如果通信速率不高,且可以接3.3V的时候,没有什么影响。

3.不是很清楚,我没见过这样用的,感觉不行。因为(1)lvds内部输入端BJT/FET要有合适的偏置或者说共模范围,单端信号是没有的,这样容易造成BJT/FET倒置等,(2)lvds实际由固定的电流驱动,在接收端有个几百欧的电阻,靠流经电阻的电流产生电压来确定信号,你这样接电流也不可控。反正你可以用信号发生器之类的接到FPGA上做个简单的实验试试。

话说FPGA不是有2.5V的LVCMOS吗?既然飞线了,为什么不飞到LVCMOS上呢?

谢谢您的回复!

首先,对于AD输出1.9V驱动FPGA3.3时,您说的对,是可以把AD的输出1.9V飞线至2.5V的IO BANK,并配置成LVCMOS25,

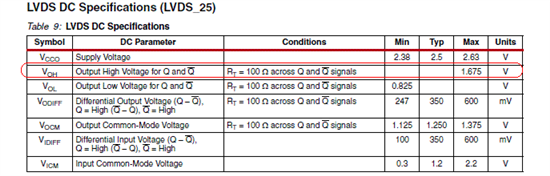

其FPGA手册中对高低电平的阀值要求如下图

这样AD 的1.9V电平(实际上可能1.65V左右)勉强可以驱动FPGA LVCMOS 2.5V的逻辑高,这样可以吗?

其次 ,对于FPGA输出3.3V驱动AD的1.9V时,像您说的即使AD有钳位,输入也不能大于VA+0.15V,因此我打算从FPGA的2.5V的IO BANK 飞线至AD的控制管脚,

并配置成LVDS25,这样相当于FPGA输出差分电平,并且只用其正端驱动 AD 的管脚,其FPGA的 LVDS25的输出电压的阀值如下图

这样就保证了FPGA的输出满足ADVA+0.15V的要求,只要 FPGA输出高电平时其差分正端不低于AD输入管脚VIH的最低值,是不是就可以了?

1.AD控制线到FPGA到lvcmos应该可以,但你别低于1.7V啊。

2.cmos连cmos,lvds连lvds。

最好还是加上电平转换器件吧