ADS8405/ADS8411 有谁有使用过么?

/CS /RD /RESET /CONVST 这些信号处理时序是怎样的,英文手册看的不清楚,水平有限。

他工作原理是如何呢

Hi

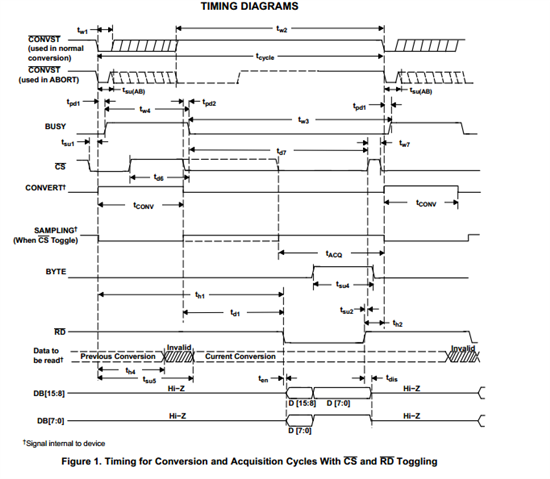

Datasheet : http://www.ti.com.cn/cn/lit/ds/symlink/ads8405.pdf 上有很多时序你可以参考:

例如:

见第九到第十二页。

Hi

或者你可以这样理解:

CS作为片选,低有效,你可以一直将其置低(接地)

CONVST 作为控制转换脚

RD可以作为数据转换完成标示脚。

从如上的时序可以看到,当convert置高开始,芯片开始转换(可选择CS置低),到转换完成要输出时RD输出第电平告诉后面的MCU(控制芯片内),此时MCU开始接收数据。

有很多种控制方式,你可以参考上述提到的控制时序。

Hi

Reset不参与时序,只是做一个内部清零的作用。

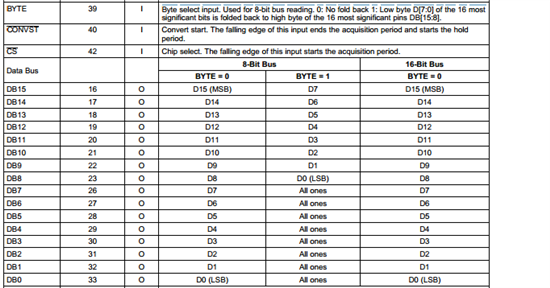

谢谢你的回复,byte一旦选定为0,是使用16字节的输出模式吧。

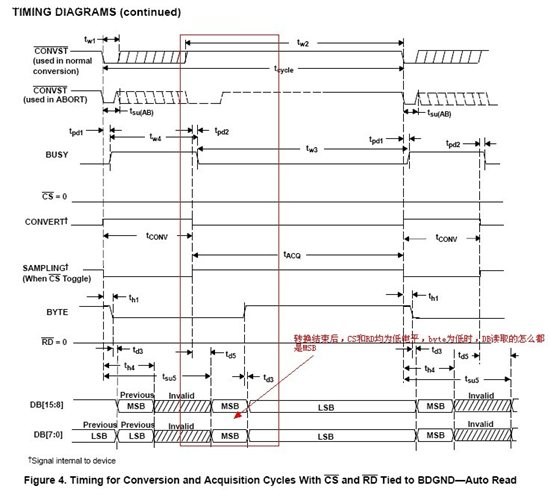

下图有点不解

谢谢你的回复,byte一旦选定为0,是使用16字节的输出模式吧。

下图有点不解

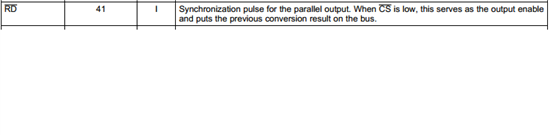

还有RD属于一个输入信号,他怎么作为数据转换完成标示脚,通知MCU转换完成呢?thank you

Hi

见Byte定义,以及数字输出:

Byte=0时,无论是8位的bus,还是16位的bus都是16位数据输出的。

Hi

是的这是个输入信号,看错成为DRDY功能。

见如下RD的定义: When CS is low, this serves as the output enable and puts the previous conversion result on the bus.

所以是当RD低的时候开始读。

RD只是一个输入的使能信号,那什么信号可以判别AD转换完成呢?。RESET是要连接复位电路吧。

见我见图红色圈出来的地方,byte为低,RD和CS都为低为何DB读的都是高位的啊?

Hi

可以通过busy信号: BUSY stays high throughout the conversion process and returns low when the conversion has ended.

同时见Td1的定义: Td1: Delay time, CS low to RD low (or BUSY low to RD low when CS = 0), min: 0nS. (针对figure1)

Busy是ADC的状态输出脚, 所以可以在busy low 后一定延时后由RD输入low, 开始接受数据。

Hi

建议看figure1~3, figure4的byte控制,确认难以看懂。

Reset 可以连接复位电路。

谢谢你,我差不多了解了。

Hi

不客气。

你好,测试过程中遇到一个问题,AD只接输入信号/convst,检测输出信号busy。测试一长段时间后,发现busy信号开始一直是正常信号,最后无信号波形,没有输出了。重启后,又好了。但长时间上电测试就会出现这个问题,就是busy信号中断,请问这个是由什么造成的呢?有哪些可能因素?实在想不出

fengxun lan

你好,测试过程中遇到一个问题,AD只接输入信号/convst,检测输出信号busy。测试一长段时间后,发现busy信号开始一直是正常信号,最后无信号波形,没有输出了。重启后,又好了。但长时间上电测试就会出现这个问题,就是busy信号中断,请问这个是由什么造成的呢?有哪些可能因素?实在想不出