模数转换芯片ADC08D500的控制引脚电平兼容和参考地问题

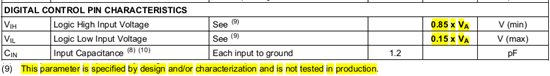

(1)ADC08D500数据手册中给出了控制引脚的VIH和VIL的下限和上限,分别为0.85*VA、0.15*VA,VA一般取1.9V,则VIH和VIL的限制分别为1.615V和0.285V。

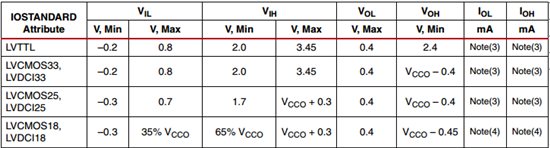

但一般我们用的微机芯片输出的1.8V LVCMOS电平都不在这个范围内,我们看到的这款器件的评估板原理图(NI 公司的BIG GIG REFERENCE BOARD REV. 2.0A)中是将这些控制信号直接与xilinx的FPGA XC4VLX15 的BANK IO直接相连,但从FPGA的参考手册中发现,1.8V LVCMOS电平并不能与之兼容,见下图。网上找到的一些电平转换芯片输出的1.8V电平也基本上是这个范围,这样一来,岂不是难有器件能够满足这款ADC的控制引脚电平要求了?另外上图中的(9)中说这个参数并未在产品中经过测试,我们不明白这意味着什么?

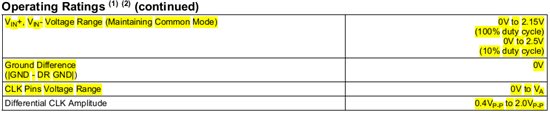

(2)ADC08D500中提到两个地(应该是数字地和模拟地)之间的压差最好为0V,不知这是否意味着需要把两个地直接相连?

你好,

关于第二个问题,在高速电路把地连起来一般也是我们EVM的做法,可以保持地的完整性和减小回流阻抗等高频问题。

关于第一个问题,一般逻辑输出会相对于负载有所变化,如果是高阻一般能输出到接近VCC,如果用满负载电流,例如16mA等,FPGA或者逻辑器件会可能降低到VCC-0.4类似的极限。这类曲线图也许是由于比较多且没什么必要放在FPGA或者逻辑器件的手册里,有的就没写,你看看能找到吗?

因为由于复杂度和成本考虑,半导体厂商不太可能在量产的时候对每个芯片全部参数值都测一遍再出厂。

你好,

“高速电路中把地连起来可以保持地的完整性和减小回流阻抗等高频问题”。我们不是很理解这句话的意思,能不能具体解释一下?

我们在实际应用中打算用0欧姆电阻将模拟地和数字地隔开,用于满足0~100mV的压差要求,这样是不是最稳妥的办法?

谢谢!

你好,

数字模拟分开主要是怕互相干扰,因为高频的电流都是有趋肤效应,而趋肤效应会使得导体高频阻抗变大,分开的后果可能导致电流走了一条阻抗比较大的路径才回到电源入口。例如强制它走过你的0欧姆电阻那条路。电流在这条路径上形成压降从而形成干扰。公用一个地平面往往可以减小这种干扰。

在高速应用中精度往往不是要求特别高,所以很多时候就让数字模拟合用一个地平面,算一个折中方法吧。实际工程中当然连还需要考虑你周边还有其他的干扰,需不需要分开,最终才能得出一个规划。

我不觉得用0欧姆来保证0V压降是最稳妥的方法,直接相连会不会更稳妥? 还是建议用EVM上的布局布线。实际中也要和你项目的具体情况进行评估折中。