关于ADS8568的一些问题

一个高速列车项目,做16通道同步数据采集节点,使用两片ADS8568,两片工作在串行模式,菊花

链方式连接,前一片的SDO_x接后一片的DCIN_x。

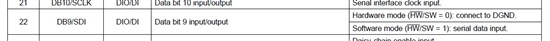

在串行软件模式下,将两片的SDI,SCLK,XCLK,BUSY,CONVST,RESET,FS都接在一起,类似

datasheet上的Figure 40,主要问题是:

1,两个芯片的SDI接在一起做相同的配置是否有问题?

2,两个芯片的BUSY接在一起是否有问题?关于各个接口的输入输出级datasheet里面都没有详细

的描述,若是推挽输出的将BUSY接在一起可能会有冲突。

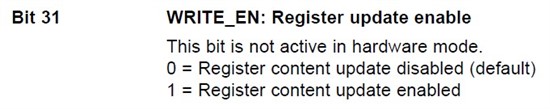

3,关于Configuration Register的配置问题,datasheet上所述的Bit31是寄存器更新使能,默认

该位为0,复位后也是0,但该位为0却是禁止更新寄存器,若是这样第一次怎么往里面写?如果说

该位为0是使能寄存器更新,为1禁止更新还能接受。毕竟芯片复位后可以往寄存器写数据,配置

好了后将该位置1,读数据时可以禁止更新寄存器避免改变寄存器的内容,因为读数据和写数据都

是用的同一个SCLK。

在串行硬件模式下,datasheet上说SDI接DGND,这样芯片就只能读数据了,通过外部引脚的连接

方式确定芯片的配置方式。但芯片内部的参考电压有个配置字,就是Configuration Register的

Bit[9:0],串行硬件模式下SDI接地无法对这个进行配置,我的理解是在串行软件模式下先配置好

这个寄存器再将其工作方式转换成串行硬件模式,但这样未免费力不讨好,毕竟SDI这条线无法省

略,还需要一条线改变~HW/HW的连接方式。同样的还是有BUSY的问题,即使对两个芯片做相同的

配置,两个芯片的转换时间总会有一点差异。是否需要将两个BUSY都接到控制器上进行或逻辑判

断?

还有一个问题就是这个芯片的转换时钟可以是内部时钟也可以是外部时钟,但是datasheet上没有

关于内部时钟的描述,只有一个内部时钟的转换时间,频率什么的都没说。这个芯片工作模式就有

四种,而且串行方式还有1线,2线,4线输出,datasheet上的描述太过简单了。项目要求pcb面积

很小,在4*5cm的板内有8颗芯片,我只能用串行模式。项目比较急了,希望TI的工程师给些指导

和建议,谢谢。

Tel:15116308141

下面是关于SDI和Bit31的描述

你的意思是片内做daisy chain然后再2片间信号再daisy chain?convst,BUSY,FS接到一起后应该不可以的,时序已经乱了。只可以片内做daisy chain吧。

“只有一个内部时钟的转换时间,频率什么的都没说”-----给了你conversion的时间,你还需要什么频率?

”个芯片工作模式就有四种,而且串行方式还有1线,2线,4线输出,datasheet上的描述太过简单了“---人家该给的描述已经给你了,你没有看懂人家而已吧。