ADS1292R DOut 乱码

本人正在使用的ADS1292R 数据转换器,配置时序后发现,读取寄存器值乱码,不知什么原因。

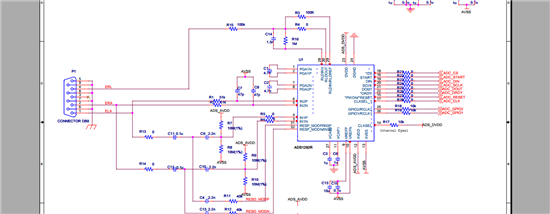

原理图

CLK_SEL脚未接

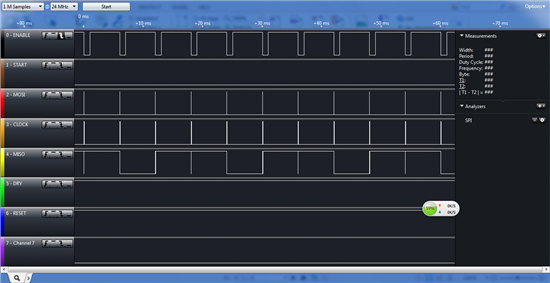

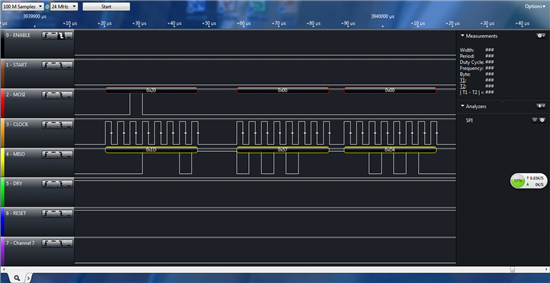

总体波形

SCLK 速率在280K上下,上电未做其他设置。

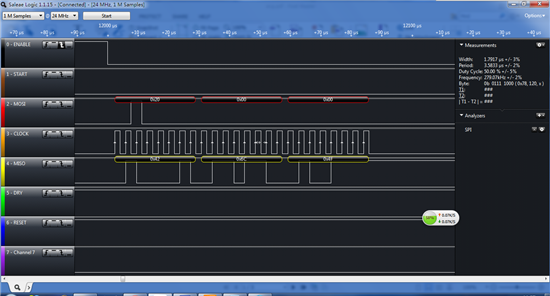

细节1

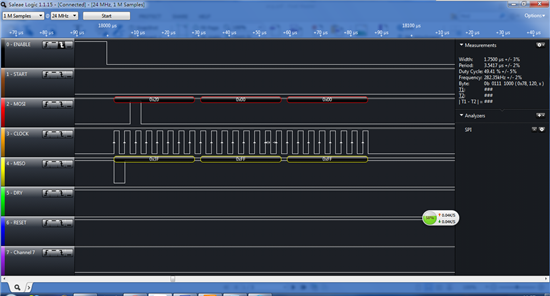

细节2

细节3

同一寄存器每次读取的值不一样,不知什么原因

读寄存器部分代码

//Chip enable

ADS1292_Enable();

SPI_I2S_SendData(SPI1,0x20 | 0x00); //Send Address

while(SPI_I2S_GetFlagStatus(SPI1,SPI_I2S_FLAG_TXE) == RESET);

SPI_I2S_SendData(SPI1,0x00); //Send num = 1

while(SPI_I2S_GetFlagStatus(SPI1,SPI_I2S_FLAG_TXE) == RESET);

SPI_I2S_SendData(SPI1,0x00);

while(SPI_I2S_GetFlagStatus(SPI1,SPI_I2S_FLAG_TXE) == RESET);

//while(SPI_I2S_GetFlagStatus(SPI1,SPI_I2S_FLAG_RXNE) == RESET);

retVal = SPI_I2S_ReceiveData(SPI1); //Read SPI

OSTimeDlyHMSM(0,0,0,1);

ADS1292_Disable();

恳请出没于TI论坛诸位大侠帮小弟一把,小弟先行谢过。

你的意思是,原理图上clksel通过10k上拉电阻到DVDD,但是实际PCB上是悬空?这个可能不行,参考手册27页,那个引脚是选择内部时钟源的。

哦,我是把17脚悬空的,也就是CLK_SEL1悬空,14脚CLK_SEL是好的。

时钟是好的,就是读寄存器不行

手册第10页图1,DIN和DOUT都是在SCLK的下降沿锁存。从你的测试图来看,2-MOSI似乎是上升沿锁存的,你再检查一下。

大侠说对了,那个设置确实不对,我后来按照手册P10说明,把CPOL 设置成了 0,CPHA 设置为1,跟手册P10的时序和约束比较了下,没有发现问题。

但是情况还是一样,能循环读出0x00,0xXX,0xff三个值,XX不定,我纳闷的是Dout在输出完数据后应该是置高才对,为什么会变低呢。

附图:

另外,时序不对这个问题还可能什么地方引起,有没有可能是芯片坏了?

前两幅图没看到~CS有跳低再跳高的波形,第三幅有。

你可以先按照手册38页图45,给32个SCLK,把读寄存器这个功能调通。

Wang大侠,貌似还不行

我大概统计了一下,是29h,31h,c0h,20h,00h,1bh,42h,8ch,3bh

共6个字节重复出现,是不是要配置什么东西?要不要换片子再试?

手册38页,首先看写寄存器,如图46。给32个SCLK,1~8个SCLK DIN写01000000,9~16个SCLK DIN写00000001,然后依次写reg data1和reg data2。

然后看读寄存器,如图45。给32个SCLK,1~8个SCLK DIN写00100000,9~16个SCLK DIN写00000001,然后从DOUT上读寄存器值。

从你的MOSI看,你在写操作的时候,1~8个SCLK写的不是0x40,而是0x20啊。你去改一下吧。

问题找着了,是ADS1292r 进入了默认的连续转换状态,读出的那六个字节值刚好是一帧数据(应该是0xc0打头)。

发了停止连续转换就能读对了。

还是要特别感谢Wang大侠的帮忙。

tuo qian大大你好

小弟目前也在使用ADS1292,現在卡住了,前面設定的部分對了,但在讀值的時候怎麼讀回來都會是80開頭,正常不是應該要C0開頭嗎

還請您幫幫忙

我写的一个笔记,你先看看

http://www.deyisupport.com/question_answer/analog/data_converters/f/58/p/25566/94621.aspx#94621

80的問題已經解決了,主要是因為地的部分沒有焊接好,導致雜訊的產生。

您的那篇文章我已經看個十來次,我一開始板子的校正就是靠您那篇來的,非常謝謝您。

目前我只用單一通道量測心電圖(CH2量測),我將心電圖模擬器產生80HR的訊號進入,量測出的數值如下

03 99 4D

03 99 4D

03 99 4D

03 54 64

03 54 64

03 54 64

03 54 64

03 7A F4

03 7A F4

03 7A F4

03 7A F4

03 7A F4

03 6E 83

03 6E 83

03 6E 83

03 6E 83

03 6E 83

03 5E 70

..

.

.

.

這些數值我用EXCEL畫出來很不像心電圖

可否指導一下?

1.首先,可能你已经做了,就是把补码转为浮点数再画图

2.用电池和多圈3296电位器做个分压,连接到采集器,最好用屏蔽线

把采集数据和用万用表-量得的数据做个对比,万用表要精度高点的

数据一致就OK了

感謝您的回覆

我的確是已經做了正負數轉換,另外我冒昧請問一下,為何還要用分壓來量測,是有要校正嗎?

可否再次麻煩您指點

在此先謝謝您

我理解的,你说采集到的信号很不像心电的意思是采集部分有问题,由于各种原因不够精确,

所以用一个足够稳定且可测的信号源来检定你的采集转换

感謝您的回覆。

小弟資質愚昧,剛才反覆想了許久,不知該如何接一個電壓進去,可否再次麻煩您為小弟解惑

感激不盡!!

大俠您好,我剛重複看了您之前那篇測試步驟,我發現到我C1,C2两端-(CH1/2 的N端和P端)对地电压,C1、C2都只有1.08V,給您我的電路圖,是不是有地方錯了?

标有NI 的 器件都不要焊

RA-LA接入电压

右腿驱动RL先不用接

您好:

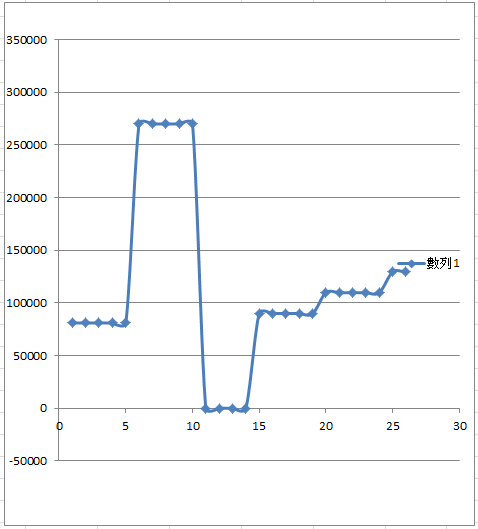

電壓量測出來是符合萬用表的值,之後我在量測心電圖將RLD開啟,圖變得比較像心電圖,我取250個點如下圖

只是我不解的地方在於明明是24bit的資料,為何畫出來的圖會像是只有4~5bit的樣子??

還是說我程式設定的流程上面有問題?

麻煩您再次解惑

感激不盡!!

你最好找个好点的信号发生器(HP或安捷伦的)试,加10mV的正弦波,

我猜是你的心电信号模拟器DA没有做模拟滤波导致的

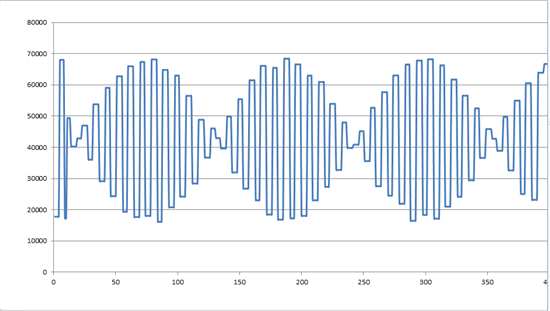

非常感謝您的回覆,我將完整的圖給您看,發現是有規律的,但真的不是心電圖

我將我流程附上,

首先我給0x11停止連續轉換

之後設定CH1為continuous mode且為500SPS

將reference buffer enabled且設為2.42V

將CH1 power down

將CH2的PGA設為1

將RLD buffer enabled且RLD connected to IN2P/IN2N

最後我設Fclk為2.048MHZ

是否有缺少甚麼流程呢??

这个不是心电信号,有点像PWM调制,电路和配置应该是没有问题的

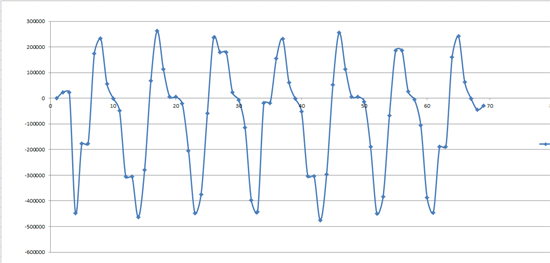

上圖為量測我自己的ECG,敢請問ADS1292有濾波的功能嗎??

能否給小弟一個方向,感激不盡!!

ADS1292内部含有一个3MHz的EMI滤波器,对低频作用不大。

你的ECG基本淹没在50Hz工频之中,这是个比较大的挑战。

估计得在PCB布板和前端模拟滤波部分多下下功夫。

感謝您的回覆

看來我得找找數字濾波

另外想再確認一下

這算是心電圖了嗎

只是為何RR波之間的間距這麼短

若以正常尚未濾50HZ心電圖來說,應該會比較漂亮點吧?!

干扰太严重的话,数字滤不干净的,而且,心电信号频谱中包含有50Hz及其谐波,50Hz频点衰减也会导致

心电波形失真。

你可以用Matlab对你采集到的数据做FFT,会发现50Hz频点增益是最强的,我大概观察了下,你信号的基本被噪声

淹没了。

多在硬件滤波下下功夫。

感謝您的回覆

小弟不是很懂,是手冊上的電路圖還需要增加濾波電路嗎?

還是說內部MUX設定的地方小弟沒有做?