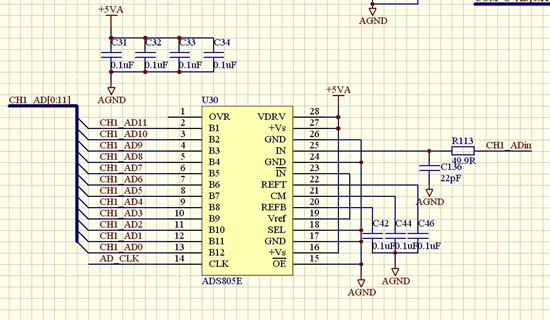

请教ads805e输出数值相比输入信号,衰减将近20%,是什么原因?

目前调试ads805e,模拟输入范围设置为0~5V,数据转换都正常,但是经过ads805e转换后的数字量,始终比输入信号小将近20%,这是怎么回事啊?之前用ads801都没有遇到这种问题?着急啊,问题都找了几天了,还没找到原因!请高手们指点迷津...

有没有测过R113左边,即IN的管脚电压, 看看是不是和你的CHI_ADin电压一样?

另外测下REFT, REFB和Vref管脚的电压看是不是正常。

用示波器测量了,R113左边和CHI_ADin电压完全一样,REFT电压=3.75V,REFB电压=1.25V;另外CM电压=2.5V,Vref电压=2.5V,电压好像是正确的?是不是还有其他问题影响输出幅度? 帮忙再分析下啊,谢谢啦。

先去掉C136,看是不是电容引起的。

如果结果还是一样,测试下+5VA波动有多大,以及AD_CLK的波形发上来。另外测试几组电压值和DAC输出值发上来看看。

去掉C136后,还是一样的,+5VA波动很小,很稳定。

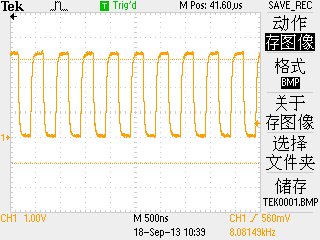

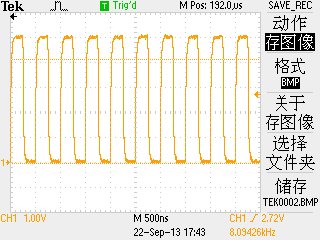

下图:为示波器捕获的ad_clk的时钟,此时钟是由FPGA分频产生的(时钟频率可调,占空比50%),提供给ad的时钟引脚。

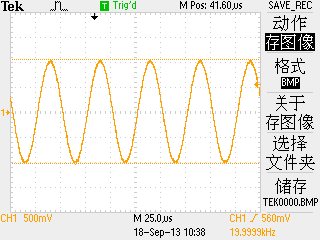

下图为输入信号波形(20KHz正弦波,安捷伦万用表测试其有效值=707mV,对应的峰峰值=707*2.828=2000mV)

下面为实测的几组数据:

测试次数 输入峰峰值(mv) 输出峰峰值(mv) 误差(%)

1 2000 1595 -20.25

2 2000 1618 -19.10

3 2000 1601 -19.95

从测试结果:可以看出输出的峰峰值均衰减了近20%,原先定型的产品用ADS801E,幅值误差很准的,但是ADS801E停产,后来就换成ADS805E,就出现此现象。麻烦帮忙分析分析,谢谢啦。

时钟似乎有问题。ADS805是个5V的ADC,CMOS的时钟看上去应该给0~5V的电平,但是现在测量到的时钟幅度只有3V左右。如果可行,看看给一个5V的时钟是否有改善。

采样4245电平转换芯片测试,还是没有改善,数值还是和之前的一样。

ad_clk波形图:

另外,怀疑芯片批次存在问题,换用了其他批次的芯片,问题依旧。

期待各位的解答。

你用稳压电源给几个直流信号进去,看看在直流情形下能否采对。另,会不会是信号源的问题?比如输出阻抗之类?做完直流测试,也可以换一台信号源试试。

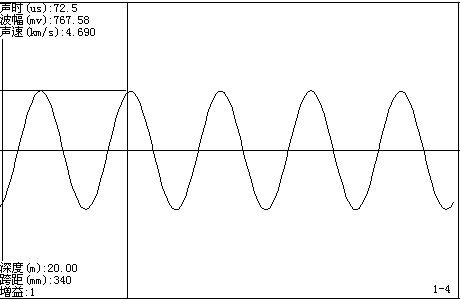

谢谢各位的悉心解答,原因已经找到了,两个ADC的量程存在微小的差别,ADS801E(量程4V:0.25~4.25),而ADS805E(量程5V:0~5.0),而软件中换算电压量时仍然采样原来的量程4V进行换算,所以显示的读数值减小将近20%。