DAC的输出杂散的来源主要在哪里?如何从应用设计上改善DAC的SFDR指标?

时间:10-02

整理:3721RD

点击:

我现在在使用DAC904E,发现其输出有一个2fs - fc的杂散,很大,导致DAC SFDR指标只有不到30dB。

如果有相应的Application Note供阅读是最好的。谢谢!

Sorry,是fs-2fc的杂散。上面笔误。

在测试中所用到的fc和fs各是多少MHz?可否上传电路图以便分析?

fs = 125MHz; fc = 50MHz。 所得杂散为25MHz,与fc幅度只差27dBc。

原理图相关信息:

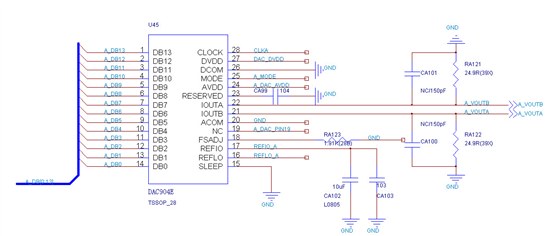

1. DAC原理图见图1.

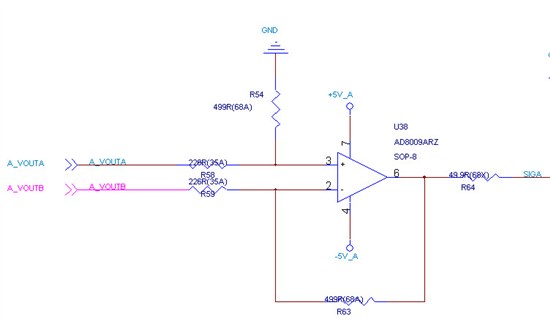

2. DAC后接了一个差动运放作为buffer,如图2

3. DAC buffer后为无源滤波器,带宽50MHz。这里没有列出图来。

图1 DAC原理图

图2 DAC buffer原理图

1. R54, R58, R59, R63这几个电阻会影响DAC输出端的匹配,建议先把R58和R59拆掉,单测DAC的输出。

2. 手册第4页典型应用电路里,RA121和RA122是50欧姆,建议你改成50欧姆试一试。

3. 如果后面一定接运放,感觉应该接成类似于仪表运放的形式,即三个运放,这样可以保证运放的输入不影响DAC的输出匹配。或者把R54, R58, R59, R63这几个电阻阻值增大,降低其对前级匹配电阻的影响。