DAC8580 fsync 与SLK怎么配合啊

时间:10-02

整理:3721RD

点击:

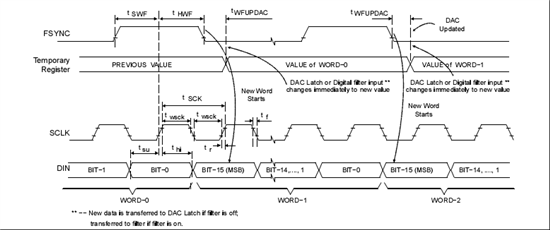

今天用51单片机驱动DAC8580,不知时序不对,还是51单片机慢了,驱动 不了啊,时序如下,请哪位大侠分析下

1. 检查FSYNC信号,从处理器每送到DAC15个数据的时候,FSYNC就要跳高一次,告诉DAC这一帧即将发完。

2. 你的数字滤波器是开还是关?如果是开,则需要有连续的SCLK。

按照时序图写的,可以驱动,但是我第一次发送一个代码如0x0f0f,第二次发送0x0a0a的时候,之间要加个延时函数,不然产生不了,为何啊

如:DAC(0x0f0f);delay(1);DAC(0x0a0a);可以工作。

DAC(0x0f0f);DAC(0x0a0a);就不能工作,没有输出。

按照手册图1所示,数据应该是连续发送的,中间不应该有延时。现在怀疑可能是数字线到达DAC时时序关系错了。你可以看到,

1. 每组16个SCLK,上升沿采数据、在第15个SCLK上升后,FSYNC给上升沿,且这个沿要超前第15个SCLK下降沿一段时间。

2. FSYNC的下降沿在第16个SCLK下降沿和下一组第1个SCLK上升沿之间。

可以发连续数据,中间不用延时,然后用示波器抓一下DAC这一侧的数字信号,看看时序上是否正确。