同一个板子上4个ADC(ADC083000)同步问题

时间:10-02

整理:3721RD

点击:

大家好,

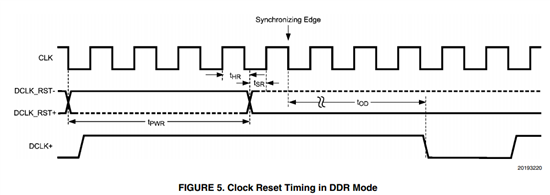

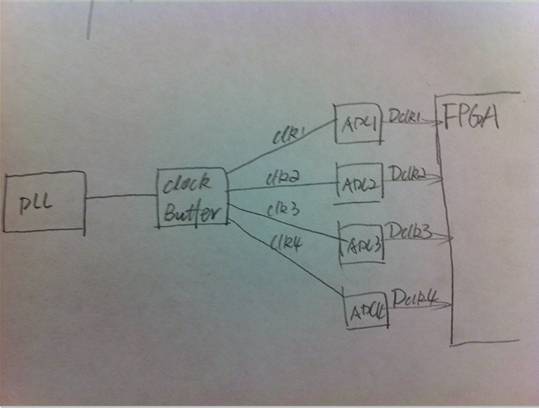

我目前采样板上有4个ADC(ADC083000), 他们都工作在3G采样上,输入时钟由同一个clock buffer 提供。 现在要将4个ADC同步以便使得4个ADC输出的时钟Dckl同步(或者说上升沿在同时刻产生)。 按照datasheet上说,可以使用CLK_RST信号同步,有时序要求如下:

The DCLK_RST pulse must be of a mini-mum width and its deassertion edge must observe setup and

hold times with respect to the CLK input rising edge.

但DCLK_RST这个时序要求是针对ADC的输入时钟而言(目前clk=1.5GHz), 特别是还有setup 和hold time要求。 这个在FPGA里面似乎是无法完成的(因为FPGA处理不了或产生不了能满足1.5GHz时钟建立和保持时间的信号,DCLK_RST)? 请问大家这个问题是怎么解决的。

谢谢了!

时序要求如下:

系统框图如下:

不确定该芯片是否对华禁运,请联系当地的TI原厂或代理商,确认没有license方面的问题或者已经签订license,然后再寻求TI的技术支持。如果在没有license的情况下使用禁运芯片,则TI不提供任何技术支持。