新手求教 ADS5521 AD转换器的一些问题,跪求各位前辈提携小弟

各位前辈、专家,我在阅读ADS5521的数据手册时,有一些问题不太懂。由于初涉硬件,缺乏经验,因此有些问题需要向各位详细请教。我截取了数据手册的部分内容,欢迎TI公司的技术支持或者乐于助人的前辈们阅读完整的数据手册,小弟在此谢过各位了!

1.关于模拟电压输入范围和参考电压的问题

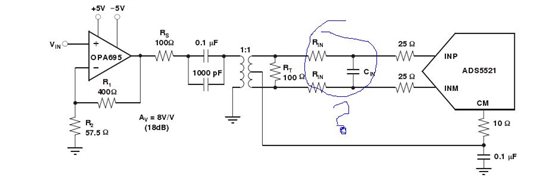

图1

手册上写,输入模拟电压范围是2.3VPP。VPP是峰峰值的意思吧。可是手册上又说CM引脚输出一个1.55V的共模参考电压信号,将该信号接到RF变压器二次侧中间抽头。这样二次侧中间抽头处的电压为1.55V,围绕1.55V 产生差分信号,输入到INP 和INM中。

图2 a

图2 b

图2 c

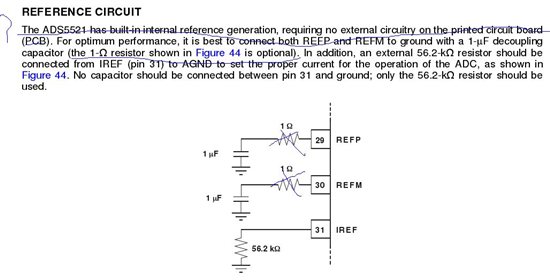

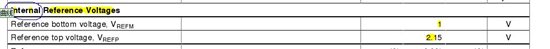

手册上说,ADS5521可以选用内部参考电压,只需将REFP和REFM通过电阻电容接地即可,便可以得到REFP 2.15V , REFM 1V,是不是不需要再设计外部参考电压输入到REFP,REFM? 可是,这样得到的是1.15V的峰峰值,电压幅值是0.575V啊?为什么手册上说是2.3VPP? 换一个说法,如果我想把一个交流正弦信号接到VIN(假如此时运放增益设置为1,),它的幅值最高可以到多少?我的理解是0.575V的幅值。这样,会围绕1.55V波动到2.15V和1V。作为初学者,我对有些概念还不是很清楚,麻烦各位了讲解一下,小弟不胜感激。

手册上说,模拟输入电压的范围不能超过参考电压的范围,也就是1V到2.15V,但是我想转换的信号是带有正负的交流信号。由于CM接到RF变压器二次侧中间抽头,把输出做了直流偏置,是不是我就可以把待测交流信号通过运放直接接到一次侧?不知道对于CM接到中间抽头,我理解的是否正确?

2.关于滤波 Rin Cin的选择

图1中的Rin Cin的大小是如何确定的?请教高手。

3.关于RESET和SPI寄存器的问题

手册上说,上电10ms以后,在reset引脚上2ms以上高电平,可以使芯片reset。之后可以使SEN有效,通过SCLK和SDATA配置SPI寄存器。RESET有效后,所有的寄存器会被赋予默认值。

图3

这是不是意味着,如果我想使用寄存器的默认值,即连续采样,60Mhz-105Mhz的采样率工作,我可以在硬件reset之后,不配置寄存器,直接读取采样值?

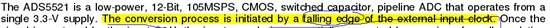

4.关于input CLK 给定时间的问题

Input CLK的给定时间有何要求?如果使用默认寄存器值时,可否在上电的同时就给clk?如果需要SEN有效,配置寄存器,clk时钟又该何时给?手册上说,clk时钟的下降沿,是转换开始的信号。

图4 a

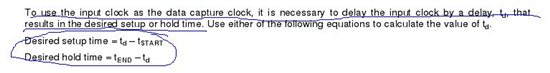

手册上说,为了使input clk 作为数据捕获信号,需要给定一个td的延时(手册第28页,第一段)。原文如图4b。这个延时td我没怎么看懂,还请高手帮助解释一下。

图4b

问题一个一个的回答你

问题1:首先,ADC的基准源是指基准电源源引脚上的电压差。如datasheet上所说。为2.15V-1V=1.15。

关于ADC的输入范围,差分输入的ADC的最大输入范围为(AIN+)-(AIN-)=2 Vref =2.3V。也就是说只要差分输入两引脚上的电压差不超过两倍的基准源,就可以进行正常转化。其中的1.55V只是给两个输入引脚提供一个共模电压。差分输入ADC是转化的,两输入引脚的电压差。其中每个一输入引脚的输入信号是以1.55V为共模信号,2.3Vpp为幅值的信号。并且,差分输入两引脚为反向。则当一个信号达到最大值时,另一个信号达到最小值时。差分信号正为2.3V

问题2:这是一个差分滤波电路,-3dB带宽为1/2*pi*2R*C.你根据你的信号频率,来设计这个电路。电阻时,不宜太大,要考虑阻抗匹配。我们的EVM板上用的就是25欧和27pF的电阻电容。

问题3. 最短复位时间是2us. 你理解的没错,流水线型ADC可以这样工作。

问题4:可以一上电就给clk,但是数据会在上电40ms后,才有效。流水线型ADC是每个时钟转化一次数据。每一次转化是由时钟的下降沿触发的。

配置寄存器,不会影响到采样的过程,只是在配置16个时钟的最后一个时钟,数据被锁存进配置寄存器。

28页说的意思时,如果使用用于ADC转化的输入时钟input clk 作为读取输出数据的时钟。需要对这个时钟进行一点延时。以达到对建立和保持时间的要求。

这是因为,从ADC收到输入时钟的下降沿到输出数据有效,是有一定的延迟的。

首先非常感谢您的回答!上周出门,没有及时回复您,非常抱歉!

对于第一个问题,您的解释我还是不大懂...简单来说的话,按照手册上的电路图,就是图1吧,若是将运放的增益设为1,可以输入的电压信号Vin是什么样的呢?比如可以是正负1.15V,或者0到2.3V? 当Vin为何值时 输出是FFF,何值时000呢? 给您添麻烦了。

问题2,3,4我都懂了,谢谢您!

关于问题3,我再确认一下:可以不配置寄存器直接进行转换,是吧?

大哥你好!首先很抱歉我不是来给你解答的,因为我是一个硬件菜鸟,我想请教你图1中各元器件的作用,比如Vin是一个正弦信号经过OPA695放大信号,之后的电阻Rs、两个电容,变压器,还有几个电阻电容是干嘛用的?我最近在做一个项目涉及到模数转换器ADS1178,对电网电压信号 进行采集,由于不会设计前级采样电路,看了你这个电路后我觉得对我有帮助但不知该电路的具体功能,大哥知道的话还望给小弟指点一二,谢谢!