dac5682z芯片配置及DA输出

想请教为何产生正弦锯齿波(即正弦波不平整,见附件)?以及DLL_LOCK有时能采样到有时采不到的情况?同事说他也以前遇到过。

具体现象是:

dac5682z的DLL_LOCK信号读出为0,但是DAC芯片两个通道能输出正常正弦波;

多次系统清零有时会产生锯齿波;

正弦波是通过两个Xilinx公司DDS IP核产生;分别输出到DATA0寄存器和DATA2寄存器;再分别输入到OSERDES进行800M数据输出;如下代码所示;

dac5682z使用400M时钟进行DDR采样;

assign DATA_TO_OSERDES[3 :0 ] = { DATA2[0], DATA2[0], DATA0[0], DATA0[0] };

assign DATA_TO_OSERDES[7 :4 ] = { DATA2[1], DATA2[1], DATA0[1], DATA0[1] };

assign DATA_TO_OSERDES[11:8 ] = { DATA2[2], DATA2[2], DATA0[2], DATA0[2] };

assign DATA_TO_OSERDES[15:12] = { DATA2[3], DATA2[3], DATA0[3], DATA0[3] };

assign DATA_TO_OSERDES[19:16] = { DATA2[4], DATA2[4], DATA0[4], DATA0[4] };

assign DATA_TO_OSERDES[23:20] = { DATA2[5], DATA2[5], DATA0[5], DATA0[5] };

assign DATA_TO_OSERDES[27:24] = { DATA2[6] , DATA2[6] , DATA0[6] , DATA0[6] };

assign DATA_TO_OSERDES[31:28] = { DATA2[7] , DATA2[7] , DATA0[7] , DATA0[7] };

assign DATA_TO_OSERDES[35:32] = { DATA2[8] , DATA2[8] , DATA0[8] , DATA0[8] };

assign DATA_TO_OSERDES[39:36] = { DATA2[9] , DATA2[9] , DATA0[9] , DATA0[9] };

assign DATA_TO_OSERDES[43:40] = { DATA2[10] , DATA2[10] , DATA0[10] ,DATA0[10] };

assign DATA_TO_OSERDES[47:44] = { DATA2[11] , DATA2[11] , DATA0[11] ,DATA0[11] };

assign DATA_TO_OSERDES[51:48] = { DATA2[12] , DATA2[12] , DATA0[12] ,DATA0[12] };

assign DATA_TO_OSERDES[55:52] = { DATA2[13] , DATA2[13] , DATA0[13] ,DATA0[13] };

assign DATA_TO_OSERDES[59:56] = { DATA2[14] , DATA2[14] , DATA0[14] ,DATA0[14] };

assign DATA_TO_OSERDES[63:60] = { DATA2[15] , DATA2[15] , DATA0[15] ,DATA0[15] };

你图上的黄色曲线是什么?DDL-LOCK如果有时告警证明时序还是有问题,不稳定.请按照手册35页上电时序操作,并保证时序.

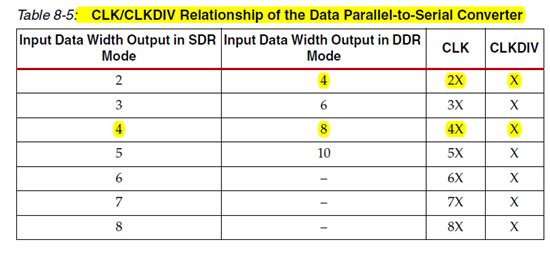

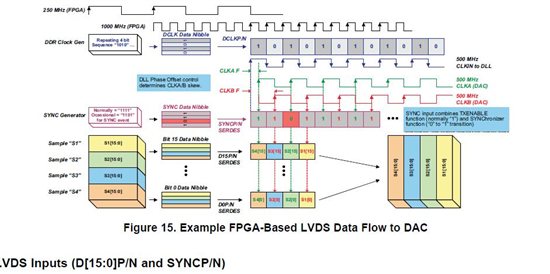

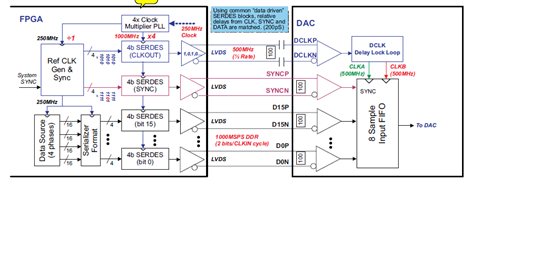

5682z的传输数据结构如下.请仔细检查

示波器输出分别是两个通道的输出,即有时会一个通道正常一个通道锯齿,当然也会有都正常或都锯齿的情况。

谢谢Robin,我下面给出一图,datasheet上的图,但我认为还是有问题的,不知理解是否正确。

图片中用到4xpll即1Ghz的时钟进入到OSERDES中,而VIRTEX5 userguide中明确说明:DDR模式中输入数据位宽4bit时CLK与CLKdiv是2X的关系,而不是4X。