DAC8581输出拉升异常

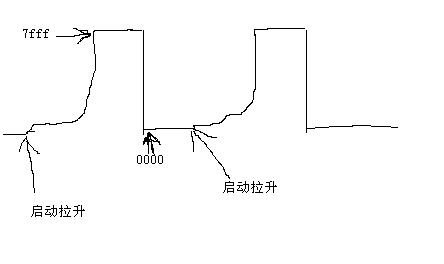

我的DAC8581,电路设计和评估板类似,输出至一片运放,发现输出波形从0直接拉升至7fff时,波形不正常,如下图:

后来将运放拆除,让DAC8581空载,测试波形还是一样;

再后来,发现只要将不一次性拉升至7fff,而只拉升至5fff这个级别,波形就正常,和手册的Figure 12一致,上升时间和下降时间都在1us内。

不知道为什么,向大神求帮助啊~谢谢~

另外,我的DAC8581工作时发热比较厉害,不知道正常与否?但是仔细测量了每一个引脚的电压和波形,都正常。

1. 类似的问题以前也有人报过,说输出最高不能摆到5V,只能摆到4.65V左右。当时的解决方法是压前面的摆幅,用后面运放补增益。就是说,从MCU过来的数字量不是从-5到+5,而是从-4到+4,或者-2.5到+2.5。。。前面损失的增益用后面的运放补回来。

2. 发热的问题建议你检查一下直流稳压电源的输出电流,看看这个电流和手册上标注的值是否一致。

非常感谢你及时的回复。

我的AVss是-5V,AVdd是+5V,Vref是+2.5V,DVdd是3.3V,我觉得这样的电源应该没有问题。

在DAC8581输出这个波形的过程中,我用示波器监测过各电源引脚,均没有抖动现象,电源应该没问题吧。

所以,从0到7fff对应的是0~2.5V的电压?前边缩小,让后面放大试试。

关于电源,我的意思并不只是让你加测电源引脚的电压,同时,你看一下电源的输出电流。5V的电压,输出10mA和输出100mA,不一样的。

是的,0到7fff是0~2.5V的电压。您的意思是,Vref继续往下降吗?比如说用1.25V,然后后面运放再多乘以一个2放大起来吗?还是说就直接放弃精度,只输出0~5fff的值,后面再放大至需要的幅度?

关于电源,我暂时还没测电流,稍后我会测一下,如果电流过大,我应该怎么处理呢?

谢谢。

我的意思不是Vref往下降,是你的输入数字信号往下降。你之前的输入是0到7fff,现在变成0到5fff或者6fff,然后再乘以一个放大器的倍数。

如果电流过大,检查一下各个引脚有没有漏电的情况。比如,可以把VREFP/N,AINP/N等输入引脚悬空,看看电流怎样变化。

那么这样不是损失了精度吗?我的输出是要慢慢调节的,有更好的解决方法吗?

谢谢。

1. 就是要损失精度换取更快的建立时间。

2. 既然输出是要慢慢调节,那为什么要跑这种从0到7fff的仿真?这种测试明显是要测大信号瞬态建立啊,和你的“输出是要慢慢调节的”不符合啊。如果你要测“输出是要慢慢调节的”,应该缓慢地改变数字输入值,然后看模拟输出的建立。

1、知道了,谢谢~

2、既然测试,我觉得就是各种情况都要试试嘛~

非常感谢你的耐心解答

我还发现,从0到8000的情况非常好,从7fff直接到8000的建立时间也非常好;只有涉及到大幅往正向跨越至7fff这种不行。

你试试看从0fff拉升到7fff时,响应时间怎样。怀疑可能是从全0输入跳到全1输入,DAC内部的电流源相当于是全开,这样电流源从电源突然抽大量电流时可能会涉及到电源的负载调整。如果从0fff跳到7fff,等于只变3位,这样电源的负载调整可能会快点。

1、刚才试了,从0fff拉到7fff,情况一样;

2、于是又试了从3fff拉到7fff,情况一样;

3、然后继续试了从70ff拉到7fff,情况一样;

期间我用示波器监控+5V电源的波形情况,一直没有任何波动。

那么我现在得出的结论就是:只要是设置到7fff,建立时间就很慢,我实测是16us的样子。

如果是这样的话,你可以试试看从0到哪一个数字值时输出不能再1us内建立。目前的结果是5fff没有问题,可以继续加大,总归有一个临界值,你应用的时候留点余量,从临界值的地方稍稍回退一点,应该就不会有问题了。

是的,目前就只有采取这种方法了。

能否帮忙做一个测试,输出增加一个2k的对GND电阻(假负载),看看输出从0跳至7fff时间上是否有改变?

原因在于无论是输出接运放还是空载,ADC的输出电流都会很小,增加负载后会有一个大的充电电流加快输出电压的上升。在datasheet中Settling time 的测试条件CL < 200 pF, RL = 2 kΩ,

DAC8581的功耗(比较大)按照175mW,热阻118°C/W,环境温度30℃,会造成芯片温度50℃左右。如果远高出就要注意是否存在电压异常了。

加上了2k负载,电压拉升波形还是差不多。

温度差不多,还不到50度。(环境温度不到30度)

刚才试了,加上了2k的电阻对地,从0到7fff的拉升波形还是一样缓慢。

温度不到50度,这样算来还算正常。

还以为没有回复成功,原来都到第二页了 -_-!

那就只能按照Decapton的方法了。谢谢回复。

温度正常,也就是排除有电压异常了。