DAC5682Z两通道输出有相差

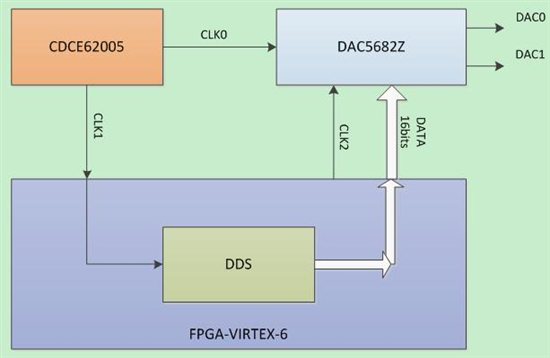

以上是我的应用场景:通过CDCE62005提供DAC5682Z的工作时钟和FPGA的工作时钟;CLK0和CLK1都是200MHz的时钟,在FPGA内部使用DDS IP核生成一个20MHz的正弦信号,通过DDR接口传递给DAC5682Z作为两个通道的数据;CLK2也是200MHz,DDR接口上升沿和下降沿发送的都是同样的数据;

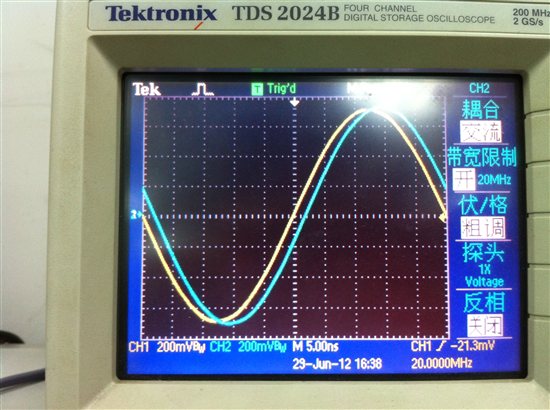

DAC5682Z配置为内插2倍模式,通过示波器观察两个通道的输出,发现两个通道有2.5ns左右的相位差异,如下图所示:

请问这个相差是在哪里产生的呢?如果减小或者消除,在我的应用环境中需要两通道的输出相差小于等于50ps,DAC5682芯片能否达到这个指标呢?

你好像用错了。

手册35页有提到“In both modes, an LVDS half-rate data clock (DCLKP/DCLKN) is provided by the user and is typically generated by a toggling data bit to maintain LVDS data to DCLK timing alignment.” 就是说,DCLKP/N的速率应该是CLKIN/C的一半。从手册38页图38的示例应用也可以看到,CLKIN/C=1GHZ,DCLKP/N=500MHz。在你的应用里,CLK0对应的应该是CLKIN/C,CLK2对应的应该是DCLKP/N,但是你把这两个时钟都设成了200MHz,这可能是通道间相位差的来源。

谢谢你的回复.

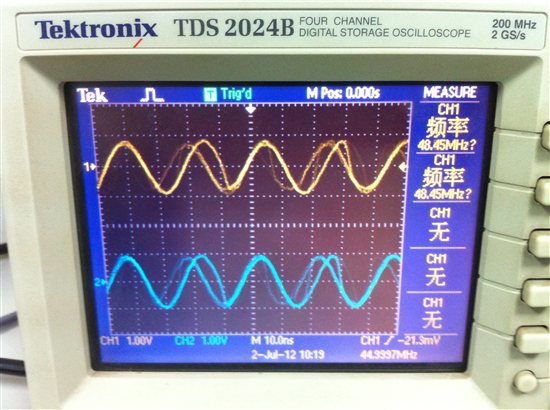

我将PLL出来给DAC芯片的时钟,也就是CLKIN/C变成400MHz,其他的时钟还是200MHz,FPGA还是用200MHz时钟产生一个20MHz的正弦信号分别送入DAC的两个通道中,得到的波形如下图所示:

从这个图上可以看出,这样配置以后输出信号的频率都不对了?

是不是我的设置那里还有问题?

谢谢

你好!

2.5ns的来源应该是由于其tpd=2.5ns,即其输出通道间存在延时,见datasheet的P8。应该是DAC5682Z达不到你的指标要求。

谢谢!

song

试一试手册第24页的config3寄存器的B_equals_A功能。看看结果是不是还是有固定的相差

我已经尝试过了B=A的设置,相位差没有变化,

因为DDR接口的上下沿都是送的一样的数据,因此应该本身两个通道就是一样的吧。

song

如果用SwapAB_out:功能后,输出的先后顺心回发生变化吗?

没有发生变化

你A/B通道发送同样的数据,SwapAB_out后没有发生变化以及B_equals_A证明这个时延来自于模拟域:

因此需要你确认下两个探头是否校准?测试匹配电路如何,测试点是否就在DAC输出口没有其他电路?

2.5ns大概为400M的一个周期,而你的DAC只有200M.

如果你的需求是要达到50ps级的相位

1.用QMC功能是DAC参考DAC3283,PAGE35调整步长为3.75度,

2.高性能专用时钟的相位调整功能也只能是ps级, 因此只能用同一个buffer并对布板提出很高要求.

你的意思是说DAC5682Z无法达到两通道的输出相位在50ps之内?

双路高速dac之间的相位误差跟很多因素有关,如温度飘移,输出匹配的设计与走线等,也有前面所说得qmc模块进行调整.

如果你对此参数要求较高,建议使用专用的高精度时钟芯片,并注意布板设计.谢谢

在DAC5682Z的芯片资料中有一个寄存器:CONFIG14:0x0E;CONFIG15:0x0F中的OffsetA[12:0]和OffsetB[12:0]是不是就是和你说的那个QMC模块功能类似?

Offset是调整直流偏置.

QMC还包括了A,B路的幅度和相位,请参考DAC3283,PAGE35的qmc_phase.此参数会受温度和输出匹配影响,

我仔细的看了QMC功能模块的资料,他这个好像是用于I Q信号之间的相位延迟,但如果我使用DAC进行输出的两个通道的信号没有正交的关系,还能用QMC进行相位控制吗?

B*QMC_PHASE[9:0] + A

可以不用完全正交但不能是不相关的信号.但是如我前面所说该参数也会受温漂和外部电路匹配等影响,因此对两路时钟相位有严格要求的应用请使用专用时钟芯片并对布板进行严格控制.谢谢

使用CMIX/FMIX后得到的信号是

Iout=Iin“*cosIF+Qin*sinIF

Qout=-Iin*sinIF+Qin*cosIF

但是在模拟域会出现offset以及mismatch,导致输出变为

Iout=offset+gainError*Iin*cos(IF-phaseError)+gainError*Qin*sin(IF-phaseError)

应用QMC可以在一定程度上减小offset,gainError以及phaseError的影响。

具体到你的应用,如果你不需要类似于上式中Iout和Qout的输出(仅仅是Iout=Iin,Qout=Qin,不做CMIX),则没必要使用QMC。